Tool/software:

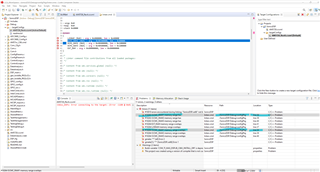

I get a Java error while updating CCS version. I will attach the screen shots once the case is created as there is no option now.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

I get a Java error while updating CCS version. I will attach the screen shots once the case is created as there is no option now.

Hi Chandran,

The update error you are seeing is an known issue on affecting certain Windows environments (https://sir.ext.ti.com/jira/browse/EXT_EP-12157). We are looking into posting an update this week that should address this issue.

Thanks,

Ricky

Hi Chandran,

Are there any other extensions that you have installed into CCS?

Patrick

I didn't add any extensions, but CCS automatically added 28 extensions as given below:

Is there a way you can just call me and we can get this done in a matter of minutes. Please call after 5PM USA Eastern time. My phone number: 248-797-9758.

The problem view error shouldn't affect updating CCS. Did you try to update to the latest v20.1.1 release mentioned by Ricky?

Where is CCS installed? Do you have admin right to write to the installation directory?

The update package for CCS v20.1.1 is not available yet, but is on track to be posted by end of week. The offline desktop install for 20.1.1 is available on ti.com here: https://www.ti.com/tool/download/CCSTUDIO

Thanks,

Ricky

Patrick Chuong Many thanks for the short call yesterday. I traced the memory range overlap and see that the memory is only defined once (ex. OCMC_RAM1 (RMX) in the linker.cmd file. However, somewhere the build tool is referring it twice and this showing that this is an error. Besides, there is no memory overflow either. Please see attached screenshots to my point above.

How was it able to build in the past in CCS Eclipse? Were you able to resolve the connection issue to the DSP core?

Would it be possible to provide the project for me to have a look? If it is ok, you can send it to me using private channel.

Hi Patrick, Many thanks for the effort. My Manager is not comfortable sharing it. Can you please call me and then we can decide which ones to send you? It is now building good in CCS 10.

Hi Patrick, Many thanks for the call this morning and for getting it compiled for both CCS 10 and 20. I measured the Reset pins, and they are OK. But I still get this error message. Any hints? I see that many users have faced the same issue from your tech support forum: Device is held in reset. Take the device out of reset, and retry the operation. - Processors forum - Processors - TI E2E support forums

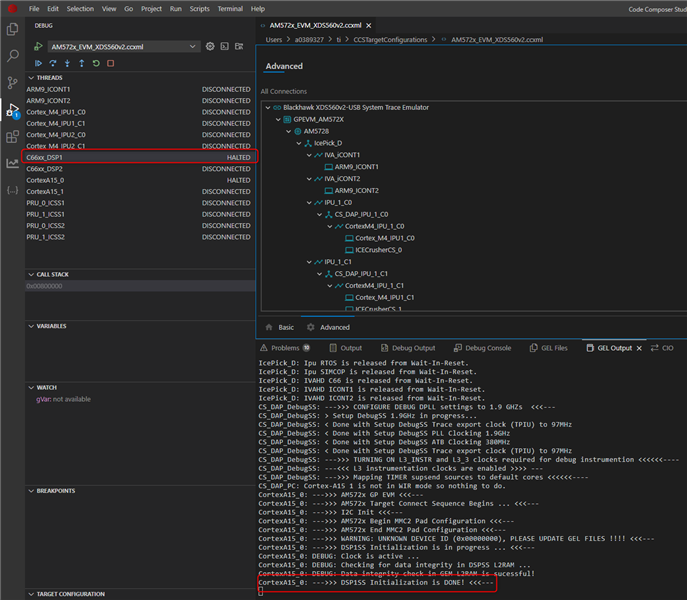

CortexA15_0: GEL Output: --->>> AM572x Cortex A15 Startup Sequence In Progress... <<<---

CortexA15_0: GEL Output: --->>> AM572x Cortex A15 Startup Sequence DONE! <<<---

C66xx_DSP2: Error connecting to the target: (Error -1180 @ 0x0) Device is held in reset. Take the device out of reset, and retry the operation. (Emulation package 9.4.0.00129)

Hi Chandran, I have reassign this thread to the Jacinto team to assist you on the debug issue.

Hi Chandran,

I have not yet used CCS 20 so not sure I can be of help with CCS per say, but the core is held in reset because you have to initialize the core first before you can load anything to it.

This was done via GEL files in the past, which I am assuming they are being used as your screenshot shows. The next step is to use the scripts to enable the core..

See the following notes taken from CCS (Eclipse)

Cortex_M4_IPU1_C0: GEL Output: --->>> AM571x Cortex M4 Startup Sequence In Progress... <<<--- Cortex_M4_IPU1_C0: GEL Output: --->>> AM571x Cortex M4 Startup Sequence DONE! <<<--- Cortex_M4_IPU1_C1: GEL Output: --->>> AM571x Cortex M4 Startup Sequence In Progress... <<<--- Cortex_M4_IPU1_C1: GEL Output: --->>> AM571x Cortex M4 Startup Sequence DONE! <<<--- C66xx_DSP: GEL Output: --->>> AM571x C66x DSP Startup Sequence In Progress... <<<--- C66xx_DSP: GEL Output: --->>> AM571x C66x DSP Startup Sequence DONE! <<<--- CortexA15_0: GEL Output: --->>> AM571x Cortex A15 Startup Sequence In Progress... <<<--- CortexA15_0: GEL Output: --->>> AM571x Cortex A15 Startup Sequence DONE! <<<--- At this point you only connected to the device.. now one connects to the a15 core: IcePick_D: GEL Output: Ipu RTOS is released from Wait-In-Reset. IcePick_D: GEL Output: Ipu SIMCOP is released from Wait-In-Reset. IcePick_D: GEL Output: IVAHD C66 is released from Wait-In-Reset. IcePick_D: GEL Output: IVAHD ICONT1 is released from Wait-In-Reset. IcePick_D: GEL Output: IVAHD ICONT2 is released from Wait-In-Reset. CS_DAP_DebugSS: GEL Output: --->>> CONFIGURE DEBUG DPLL settings to 1.9 GHZs <<<--- CS_DAP_DebugSS: GEL Output: > Setup DebugSS 1.9GHz in progress... CS_DAP_DebugSS: GEL Output: < Done with Setup DebugSS Trace export clock (TPIU) to 97MHz CS_DAP_DebugSS: GEL Output: < Done with Setup DebugSS PLL Clocking 1.9GHz CS_DAP_DebugSS: GEL Output: < Done with Setup DebugSS ATB Clocking 380MHz CS_DAP_DebugSS: GEL Output: < Done with Setup DebugSS Trace export clock (TPIU) to 97MHz CS_DAP_DebugSS: GEL Output: --->>> TURNING ON L3_INSTR and L3_3 clocks required for debug instrumention <<<<<<---- CS_DAP_DebugSS: GEL Output: ---<<< L3 instrumentation clocks are enabled >>>> --- CS_DAP_DebugSS: GEL Output: --->>> Mapping TIMER supsend sources to default cores <<<<<<---- CS_DAP_PC: GEL Output: Cortex-A15 1 is not in WIR mode so nothing to do. CortexA15_0: GEL Output: --->>> AM571x Target Connect Sequence Begins ... <<<--- CortexA15_0: GEL Output: --->>> AM571x PG2.0 GP device <<<--- CortexA15_0: GEL Output: --->>> PRCM Clock Configuration for OPPNOM in progress... <<<--- CortexA15_0: GEL Output: Cortex A15 DPLL OPP 0 clock config is in progress... CortexA15_0: GEL Output: Cortex A15 DPLL is already locked, now unlocking... CortexA15_0: GEL Output: Cortex A15 DPLL OPP 0 is DONE! CortexA15_0: GEL Output: IVA DPLL OPP 0 clock config is in progress... CortexA15_0: GEL Output: IVA DPLL OPP 0 is DONE! CortexA15_0: GEL Output: PER DPLL OPP 0 clock config in progress... CortexA15_0: GEL Output: PER DPLL already locked, now unlocking CortexA15_0: GEL Output: PER DPLL OPP 0 is DONE! CortexA15_0: GEL Output: CORE DPLL OPP 0 clock config is in progress... CortexA15_0: GEL Output: CORE DPLL OPP already locked, now unlocking.... CortexA15_0: GEL Output: CORE DPLL OPP 0 is DONE! CortexA15_0: GEL Output: ABE DPLL OPP 0 clock config in progress... CortexA15_0: GEL Output: ABE DPLL OPP 0 is DONE! CortexA15_0: GEL Output: GMAC DPLL OPP 0 clock config is in progress... CortexA15_0: GEL Output: GMAC DPLL OPP 0 is DONE! CortexA15_0: GEL Output: GPU DPLL OPP 0 clock config is in progress... CortexA15_0: GEL Output: GPU DPLL OPP 0 is DONE! CortexA15_0: GEL Output: DSP DPLL OPP 0 clock config is in progress... CortexA15_0: GEL Output: DSP DPLL OPP 0 is DONE! CortexA15_0: GEL Output: PCIE_REF DPLL OPP 0 clock config is in progress... CortexA15_0: GEL Output: PCIE_REF DPLL OPP 0 is DONE! CortexA15_0: GEL Output: --->>> PRCM Clock Configuration for OPP 0 is DONE! <<<--- CortexA15_0: GEL Output: --->>> PRCM Configuration for all modules in progress... <<<--- CortexA15_0: GEL Output: --->>> PRCM Configuration for all modules is DONE! <<<--- CortexA15_0: GEL Output: --->>> DDR3 Initialization is in progress ... <<<--- CortexA15_0: GEL Output: DDR DPLL clock config for 666MHz is in progress... CortexA15_0: GEL Output: DDR DPLL clock config for 666MHz is in DONE! CortexA15_0: GEL Output: Launch full leveling CortexA15_0: GEL Output: Updating slave ratios in PHY_STATUSx registers CortexA15_0: GEL Output: as per HW leveling output CortexA15_0: GEL Output: HW leveling is now disabled. Using slave ratios from CortexA15_0: GEL Output: PHY_STATUSx registers CortexA15_0: GEL Output: --->>> DDR3 Initialization is DONE! <<<--- CortexA15_0: GEL Output: --->>> Mapping TIMER supsend sources to default cores <<<<<<---- CortexA15_0: GEL Output: --->>> IPU1SS Initialization is in progress ... <<<--- CortexA15_0: GEL Output: --->>> IPU1SS Initialization is DONE! <<<--- CortexA15_0: GEL Output: --->>> IPU2SS Initialization is in progress ... <<<--- CortexA15_0: GEL Output: --->>> IPU2SS Initialization is DONE! <<<--- CortexA15_0: GEL Output: --->>> DSP1SS Initialization is in progress ... <<<--- CortexA15_0: GEL Output: DEBUG: Clock is active ... CortexA15_0: GEL Output: DEBUG: Checking for data integrity in DSPSS L2RAM ... CortexA15_0: GEL Output: DEBUG: Data integrity check in GEM L2RAM is sucessful! CortexA15_0: GEL Output: --->>> DSP1SS Initialization is DONE! <<<--- CortexA15_0: GEL Output: --->>> IVAHD Initialization is in progress ... <<<--- CortexA15_0: GEL Output: DEBUG: Clock is active ... CortexA15_0: GEL Output: --->>> IVAHD Initialization is DONE! ... <<<--- CortexA15_0: GEL Output: --->>> PRUSS 1 and 2 Initialization is in progress ... <<<--- CortexA15_0: GEL Output: --->>> PRUSS 1 and 2 Initialization is in complete ... <<<--- CortexA15_0: GEL Output: --->>> AM571x Target Connect Sequence DONE !!!!! <<<--- Then find the menu above that has Scripts-->AM57x_MULTICORE Initialization-->DSPSSClkEnable_API Should look like this: GEL Output: --->>> DSP1SS Initialization is in progress ... <<<--- CortexA15_0: GEL Output: DEBUG: Clock is active ... CortexA15_0: GEL Output: DEBUG: Checking for data integrity in DSPSS L2RAM ... CortexA15_0: GEL Output: DEBUG: Data integrity check in GEM L2RAM is sucessful! CortexA15_0: GEL Output: --->>> DSP1SS Initialization is DONE! <<<---

Hi Josue, One of our engineers also hinted at the GEL files. My question is, why now? This was working last week...perhaps some GEL files (whatever they are and do) got deleted during clean up and migration? In any case, can you please send me the files and the location they need to go.

Same setup doesn't work anymore. It does work for another engineer (whose setup I was =using) but he won't be back until Tuesday (April 8). Can you please call me so we can take care of this quickly?

Chandran,

This does not make sense...

My question is, why now? This was working last week...perhaps some GEL files (whatever they are and do) got deleted during clean up and migration? I

Something in your setup was releasing the core from reset, this doesn't just happen. Please take note of the exact procedure being followed in the working scenario.

CCS 20.x is not officially used to test AM57 officially yet so I do not have experience with it, therefore I cannot be of much help here. Please read the documentation that accompanies the CCS release.

-Josue

This is 'not' a HW issue, and the device is not in Reset. Because, Test connection works clean for all cores. Please see good results below:

Chandran,

This only proves that the SoC is functional and the connections/interconnects in the device are all functional. The SW deployed is what sets/releases the cores from reset. If you are using GEL files/ or no-boot mode, then you have to use the same GEL files to release core from reset.

On another note, is this migration to CCS 20 needed? Support for TI-RTOS has been deprecated in these releases.

Are you using another OS?

-Josue

Please note this issue exists in CCS Version 10.x also. Yes, we use TI RTOS. I believe this is a glitch/ vulnerability in TI tool chain that is causing us a lot of harm and loss of productivity. We now have 3 boards, and all have the same issues, in 2 different physical locations. They all function but we just can't debug. Please talk to the experts and get back to me with a phone call at 248-797-9758.

Chandran,

Please share your exact procedure

See the following documentation: software-dl.ti.com/.../AM572x_GP_EVM_Hardware_Setup.html

-Josue

Hi Josue, We are 'not' back to version 6. Please see my logs above on communication and call me to take care of this.

Chandran,

Your logs show me that your device is in reset..

C66xx_DSP2: Error connecting to the target: (Error -1180 @ 0x0) Device is held in reset. Take the device out of reset, and retry the operation. (Emulation package 9.4.0.00129)

The documentation I shared above explains how to do the following in the video attached:

Best,

Josue

The same process was tried by your colleague Patrick and the issue is not resolved. Besides the Reset is a bogus error message -there is no physical reset in the board and I stated this earlier. We need to ensure that the GEL files are correctly executed. If you are confident of resolving this issue, you need to pick up the phone and call me NOW and stop this unnecessary useless chasing the ghost stuff. I will have no option but to escalate to your higher CEO through our CEO as we expect a better and quicker solution being a regular customer. We also have a decision to make on which micro to use for our future products due to this poor tech support.

Chandran,

I will inform my management of your situation. Please send me your email over private message and I can arrange a proper business call.

Have you contacted your local FAEs?

-Josue

Sorry Josue, I haven't received any meeting invite yet. I just refreshed my Inbox. Here is the one I have set it up which also we can use.

_______________________________________________________________________________

Microsoft Teams Need help?

Meeting ID: 291 439 458 564 2

Passcode: iA7Dy7fZ

Dial in by phone

+1 872-212-4377,,362090521# United States, Chicago

+506 4102 3318,,362090521# Costa Rica, All locations

+44 20 3443 9384,,362090521# United Kingdom, City of London

+40 21 529 2063,,362090521# Romania, Bucharest

+91 22 6001 1904,,,,362090521# India, Mumbai

+63 2 8231 3217,,362090521# Philippines, Manila

Phone conference ID: 362 090 521#

For organizers: Meeting options | Reset dial-in PIN

________________________________________________________________________________

Best regards,

Chandran Palanisamy | Senior Electrical Engineer (Model based Development) | Branson Welding & Assembly

Emerson Automation Solutions | 46280 Dylan Dr #100 | Novi, MI 48377, USA

+1 (248) 797-9758

Chandran,

Based on our meeting online meeting, I observed that the issue was that the cores were not initialized.

After helping you set up the target configuration, we validated that you were able to connect core.

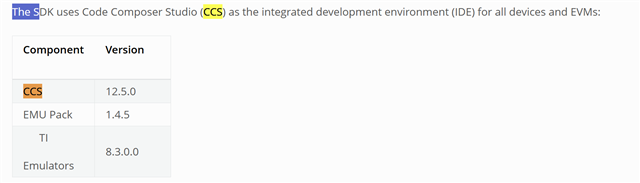

I consider this thread as resolved. Keep in mind that CCS20 is not supported by AM57x at this time.

For the supported CCS versions plese see the SDK release notes

https://software-dl.ti.com/processor-sdk-rtos/esd/AM57X/09_03_00_00/exports/docs/devices/AM57X/rtos/Release_Specific_Release_Notes.html

Best,

-Josue

Keep in mind that CCS20 is not supported by AM57x at this time.

Just to clarify, CCS 20 does technically have debug support for AM57x. I was able to create a configuration and launch a debug session for an AM572x EVM configuration, connect to the A15, then use the GEL hotmenu to pull the DSP out of reset and then connect to the DSP.

So while debug is possible with CCS 20, whether it is recommended (supported) by the device team is another story.

Thanks

ki