Other Parts Discussed in Thread: ADS127L11,

Tool/software:

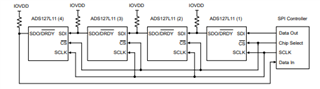

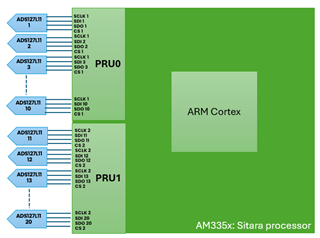

We want to interface 20 nos. of ADS12L11 ADCs to PRU of Sitara processor.

We want to achieve sampling rate of 100 ksps with above architecture with parallel sampling. Can you please let us know whether is it feasible?

To keep additional processing power for future scope, we are thinking to use AM64xx sitara. However, is AM64x support QNX?

AM64x support quad core cortex R5F and dual core cortex A53 as well. So is it possible to run QNX on R5F and Linux on A53? Anyone using this way?

Thanks and best regards,

Dnyandeep