Tool/software:

We want to use SPI NOR flash to boot from on our custom board based on AM62x.

Ref: software-dl.ti.com/.../UG-QSPI.html

We are trying to flash QSPI NOR using SD card referring to above document

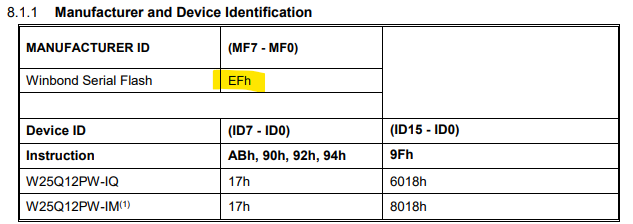

We are using Winbond W25Q01JVSFIQ SPI Flash

For that, we have made some changes in the device tree.

We have added MTD support for Winbond, and added UBIFS support in uboot and kernel menuconfig.

on probing in u-boot, we are getting this error:

=> sf probe

jedec_spi_nor flash@0: unrecognized JEDEC id bytes: ff, ff, ff

Failed to initialize SPI flash at 0:0 (error 0)

Can you suggest what we are missing.

And hardware / software changes required to boot from SPI Flash?

Also, can you suggest which image we can use if we are directly flashing to SPI NOR using SPI NOR Flash Programmer ?