Tool/software:

We need the clarification urgently!

LPDDR4 configuration settings queries.

We sent a Toyota PWB populated with MT53E256M32D1KS-046 AAT:L to Micron for LPDDR4 testing and provided the SW image with the attached DDR configuration, below is their findings:

1. Training Summary:

1a. Write Leveling: MR2 bit 7 is NOT set-> unanswered. Pls clarify what needs to be done.

1b. NO MR4 read command observed during initialization and normal operation->As per TI's response we got to know that it will be planned in future SDK release. In which SDK release this feature will be handled?

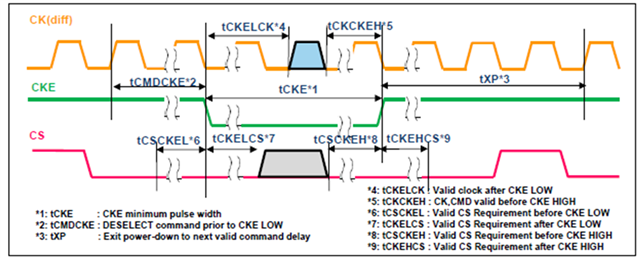

2.They couldn’t perform measurements on tCKCKEH, tCKELCK, tCMDCKE and tXP since CKE was always high

3. Self refresh:

tREFIpb and tPBR2PBR: Refresh PB command was not observed

tSR, tXSR and tESCKE: self-refresh command was not observed

Regards,

Vishwajit V K