Part Number: PROCESSOR-SDK-AM64X

Tool/software:

I am using a combined boot flow. SBL is running from R5 single core. the other core are not used.

Question,

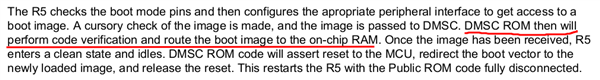

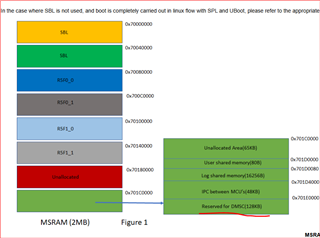

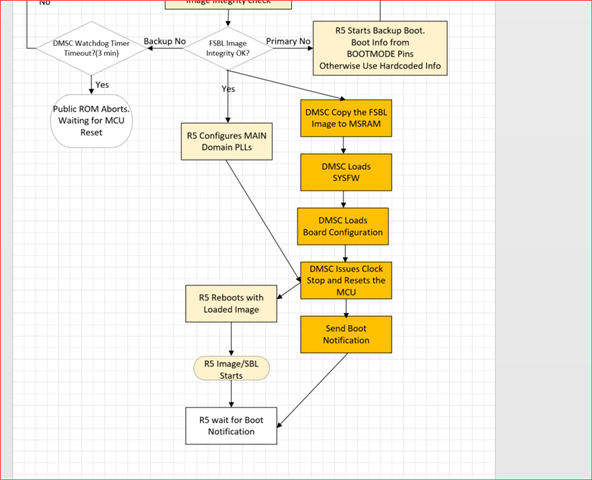

1.In xSPI boot mode, at which step DMSC RBL copy the image to MSRAM vis SPI ? I believe it happened before step "DMSC Releases Reset to R5 CPU",

2. since it is combined boot flow, SYSFW should be decrypted and load at above place. after booted SYSFW and loaded board configuration it will send boot notification.

3. then R5 start assebmly and boot to main, tjem ot wait for boot notification.

Please confirm

Thanks.