Tool/software:

Hello,

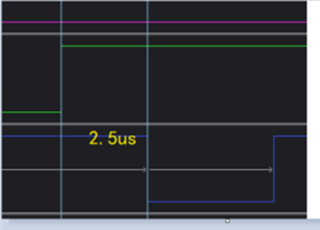

I am using SDK version 8.6, booting R5F via A53, with IPC (Inter-Processor Communication) involved. During operation, I found that the delay time from detecting a change at a hardware IO port to the start of entering the interrupt handling function is unstable. Sometimes it is over 500 nanoseconds, and sometimes it can reach 1 microsecond or even 2 microseconds. I measured this using a logic analyzer and by toggling the IO pin level within the interrupt entry function. This situation occurs when the R5F core is running on DDR. When I do not use A53 to boot R5F and instead run the entire program from MSRAM, the measured results are also unstable. I am quite confused about this part. Can you help analyze it? Even with stack operations during this process, could such a large delay occur? It is worth noting that the priority of the external interrupt I am using is set to 0, which should be the highest priority.

The rising edge of the green (signal) is the actual moment when the hardware external interrupt arrives, and the falling edge of the blue (signal) is the moment when the interrupt handling function is just entered.

The entire program comprises three tasks:

- UART data processing task:

- Priority: 30

- UART uses interrupt-driven reception, with an interrupt priority of 4.

- SPI wireless module communication task:

- Priority: 33

- Processed only once every 2 seconds, using polling mode for SPI communication.

- LED control task:

- Priority: 25

This configuration balances real-time responsiveness (e.g., UART handling higher-priority interrupts) with periodic background tasks (SPI) and low-priority visual feedback (LED control).

Glad to receive your message!