Tool/software:

Dear Expert,

Once DRAM in-line ECC enabled, R5 u-boot will initial write ECC protected area in advance.

It will increase system boot latency (even with BIST module initial write) and not friendly to user experience.

To reduce boot latency, I have a idea to postpone ECC protected area initial write behavoir from R5 u-boot stage to post-boot stage (e.g, after Linux boots up)

Given SoC RMW (read-modify-write) policy on ECC protected area, it means,

- After system boots up, if I initial write specific patten to ECC protected area (which is not initial written in R5 u-boot, to reduce boot latency)

- There will be read ops ahead of write ops due to RMW, and this extra read ops will get garbage data and generate ECC error interrupt.

My workaround solution is that, after system bootup, disable ECC interrupt before initial write ECC protected area, then resume ECC interrupt after initial write.

Then I do below experiment in SDK ti-processor-sdk-linux-adas-j721e-evm-10_01_00_04

in R5 u-boot stage,

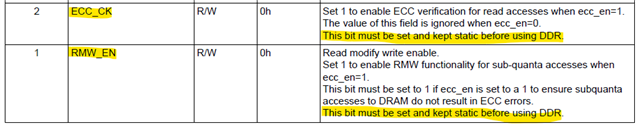

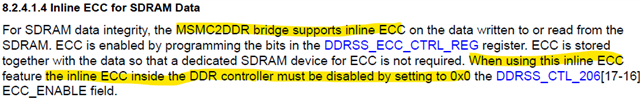

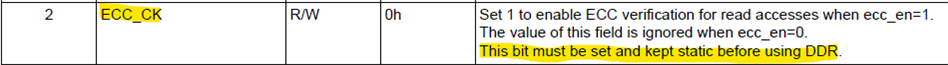

- add ti,ecc-enable = "true" and ss_cfg register range into k3-j721e-ddr.dtsi to enable in-line ECC function in MSMC2DDR bridge

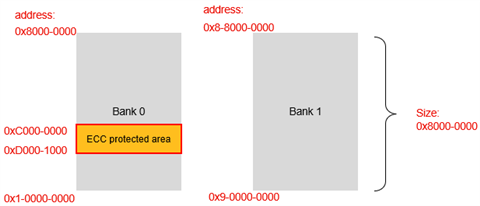

- configure ECC protected area 0xC000-0000 ~ 0xD000-1000

- then initial write DRAM area 0xC000-0000 ~ 0xD000-0000 with specific patten 0x12345678deadbeef

- that is to say, 0xD000-0000 ~ 0xD000-1000 is ECC protected, but not initial written.

in A72 u-boot stage,

| => md.l 0xc0000000 0x4 // 0xC000-0000 ~ 0xD000-0000 already be initial written c0000000: deadbeef 12345678 deadbeef 12345678 ....xV4.....xV4. |

| => md.l 0x029800a8 0x1 // DDRSS_V2A_INT_SET_REG, find ECC interrupt enabled 029800a8: 00000038 // 0x38 means multi 1-bit/1-bit/2-bit error interrupt enabled => mw.l 0x029800ac 0x38 0x1 // DDRSS_V2A_INT_CLR_REG, write 0x38 to disable ECC interrupt => md.l 0x029800a8 0x1 // DDRSS_V2A_INT_SET_REG, now ECC interrupt disabled 029800a8: 00000000 |

|

=> mw.l 0xd0000000 0x12345678 0x1000 // Try to initial write ECC protected area 0xD000-0000 ~ 0xD000-1000 x0 : 0000000000000faf x1 : 00000000d0000144 Code: d2800001 94029cfd 93407e82 aa1303e1 (d1000400) resetting ... |

Then here are my questions:

- When ECC interrupted disabled, why initial write will cause exception ? how to avoid or handle such exception ?

- Is there any ECC error handle sample code for MSMC2DDR bridge ?

BTW, I already find ECC error handle sample code in ti-processor-sdk-rtos-j721e-evm-10_01_00_04/sdl/examples/ecc

But it leverages ECC implementation in DDRSS, not follow the recommendations in SDK doc

ECC error handle sample code for MSMC2DDR brige will be appreicated :-)

I'm looking forward to your feedback.

Thanks.