Tool/software:

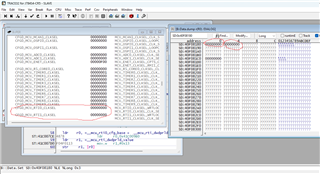

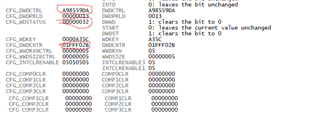

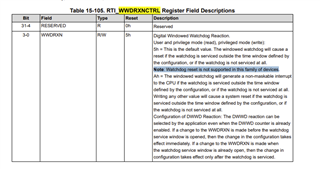

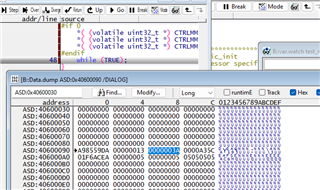

RTI_WWDRXNCTRL Register (0x406000A4) is 05H, watchdog timeout action is reset the system

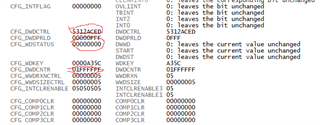

RTI_WDSTATUS Register (Offset = 98h) [reset = 0h] is 0x3A now, indicates that there are watchdog timeout, and multiple watchdog violation events happened. The system should reset with this status, but board is NOT reset; it keeps looping there.