Tool/software:

Hello,

I would like to confirm which information is correct.

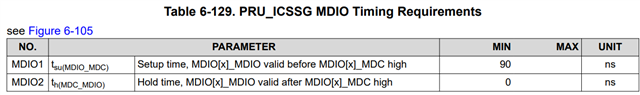

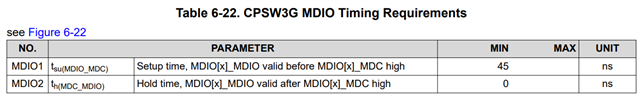

* According to datasheet, there is following two spec.

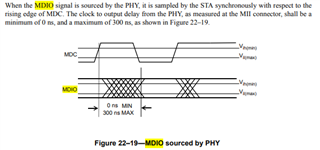

From datasheet, I understand that MDIO read value at MAC side is latched based on MDC rising edge.

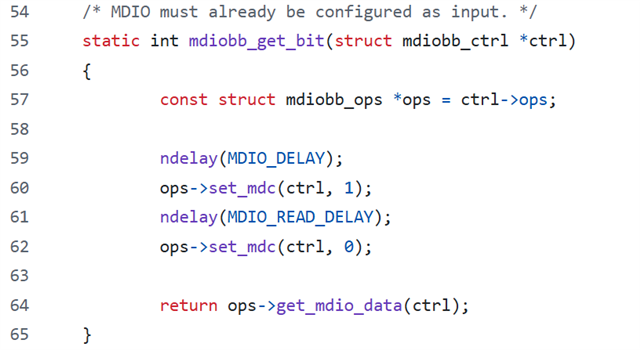

However, according to linux driver for MDIO, it seems that read value is latched based on MDC falling edge.

I'm confusing which information is correct from viewpoint of MDIO read at MAC side (AM64xx).

Could you please give your opinion about this ?

Best Regards,