Tool/software:

256KB SRAM memory system divided into two banks

– 192KB of instruction code (I-RAM)

– 64KB of data space (D-RAM)

Hello TI expert,

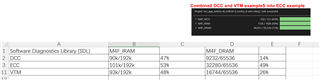

We are doing the development of SDL on M4F, there are some examples provided by TI.

When I integrate three of them, I find that the D-RAM is really not enough for developing with our application software.

I have the concern, does TI have data information about the RAM space needed for all SDL examples?

Or If the D-RAM is not enough for development for SDL, which memory could M4F use?