Tool/software:

Hi team,

I found these two registers in TRM:

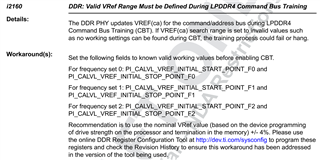

PI_CALVL_VREF_INITIAL_START_POINT

PI_CALVL_VREF_INITIAL_STOP_POINT

What is the range value of HEX in these two registers?

How should I modify if I want to increase the training range?

(ex: DDRSS_PI_207_DATA 0x321E3200)

Thanks.

Maurice