Other Parts Discussed in Thread: DRA821,

Tool/software:

Champs,

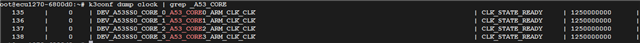

By using K3conf in AM67x pre-build image on AM67x EVM, the A53x clock are running only 1.25Ghz.

How to change the A53 clock from 1.25Ghz to 1.4Ghz?

Also what the setting (temperature thread hold) in Linux to reduce clock rate when SOC die temperature reach high (setting) temperature for thermal protection and reduce power consumption?

By checking Linux SDK document, not seeing similar topic for power management like AM62x as below line for reference.

Only power management and thermal related chapter in AM67x is VTM, but DFS chapter is blank or not be able to connect.

Could team point us to related document and setting on how to do ARM A53 clock setting and power management policy?

BR, Rich