Tool/software:

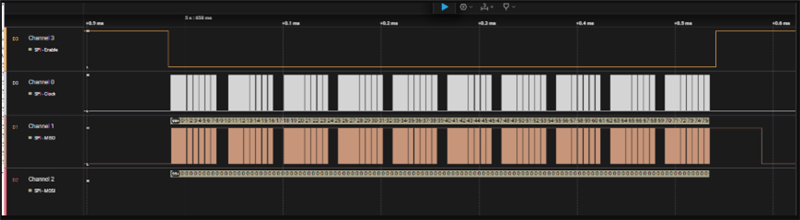

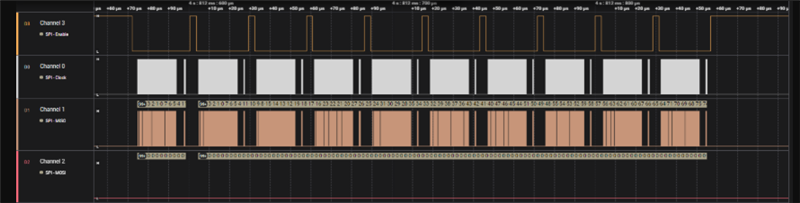

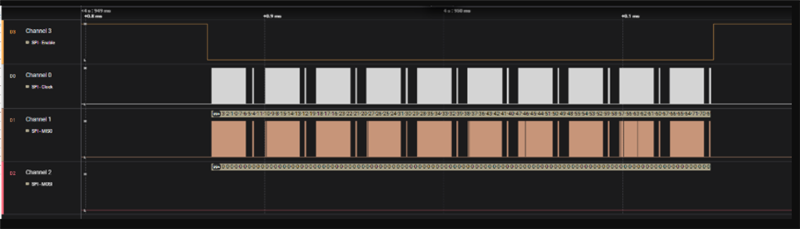

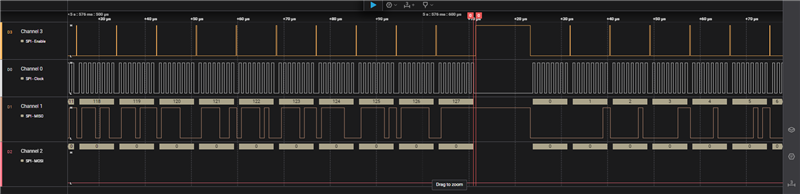

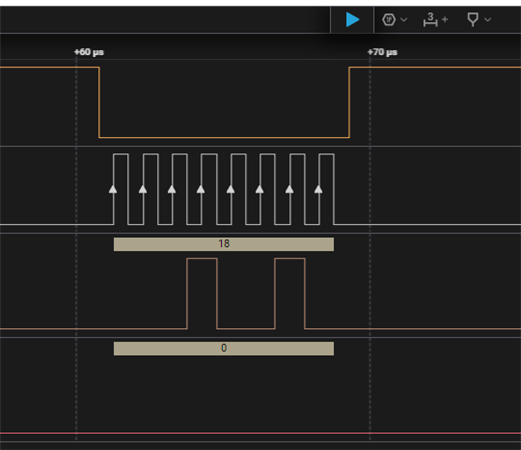

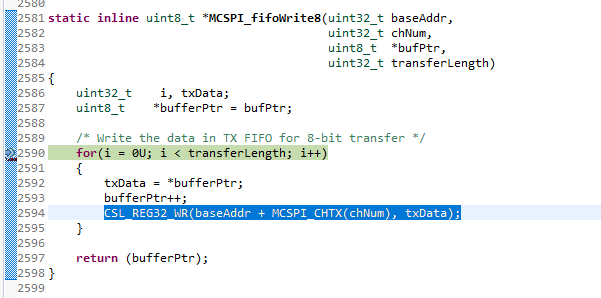

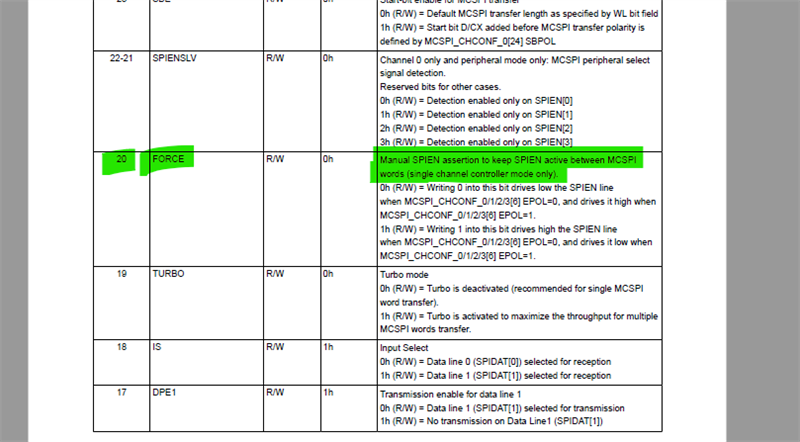

I have an MCSPI transaction that I am performing. The data size is 8 bits, and i want to transmit 3 consecutive frames without disabling CS in between them. This is required by the hardware.

I try setting csDisable = FALSE, which seems to do nothing. I have a multi-controller SPI setup. Channel 0 does not require this and works fine, but channel 1 requires this and is not working. Im using the LLD not the HLD.

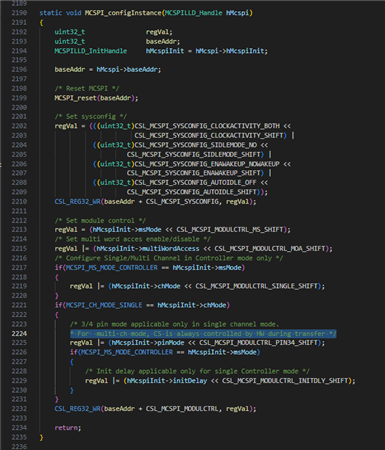

MCSPI config: