Tool/software:

Dear Champ,

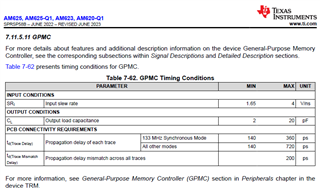

On AM625 Data Manual GPMC timing conditions table, it indicates PCB CONNECTIVITY REQUIREMENTS.

For Td (trace delay), Propagation delay of each trace, for 133Mhz, Min 140 ps and Max 360 ps.

Is this characteristic for PCB it self which the stackup and layout trace propagation delay need to within the range?

Is not ruling the delay create by the total trace length, right?

Next parameter Td(Trace Mismatch Delay), Max 200 ps, what's the definition of Mismatch?

Mismatch between each signal trace length? 200ps could be 1000mil difference on trace length.

I think the mismatch here should not be the trace length difference.

Is the characteristic for PCB layout trace equivalent propagation delay based on its stack and trace width and reference layer?

The last, is there trace length limitation for GPMC?

BR, Rich