Part Number: PROCESSOR-SDK-AM62X

Other Parts Discussed in Thread: AM6252, AM62P

Tool/software:

DearTI,

we have an issue with the AM6252 board (own product, not Dev Kit).

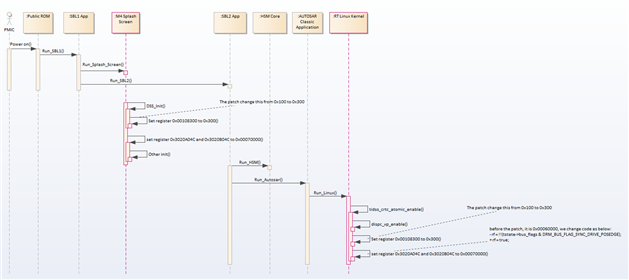

According to the datasheet we should set the following HSYNC/VSYNC control DSS0 pins:

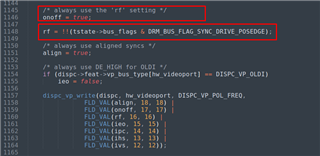

In TI code this seems to be the case the applicable register is configured correctly:

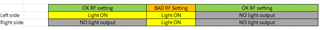

We performed the following 2 tests:

1. Using default code (as above):

Registers seem to be set ok.

Oscilloscope is showing VSYNCH signal transition on falling edge:

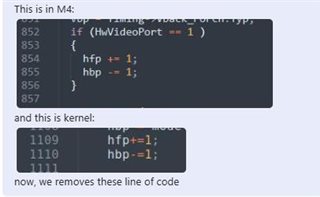

2. Modified code to set the RF to NEGATIVE edge:

The register seems to be set correctly.

When measuring the VSYNCH signal we see the VSYNCH STILL being driven on the falling edge though:

It currently seems changing the RF in VP2_FREQ register setting has no effect!

Are we missing something?

We're looking forward to your feedback.

Thank you in advance!

M.Kubica