Tool/software:

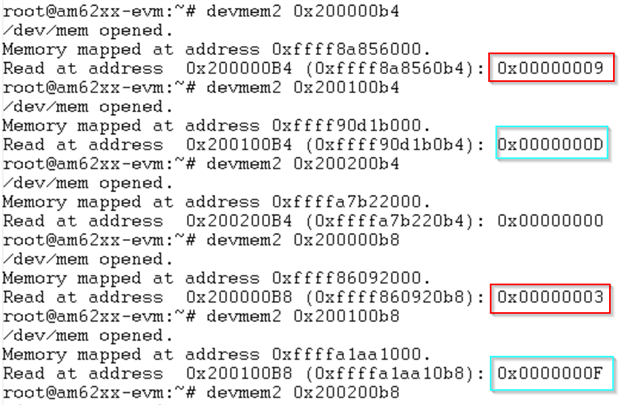

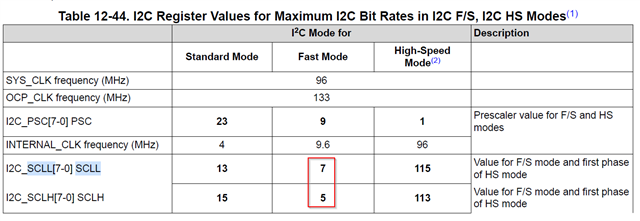

According to TRM, in 400KHz fast mode, SCLL=7, SCLH=5, but read back register SCLL=9, SCLH=3. From SDK8.3 and SDK9.2.

While standard 100KHz configuration is same as TRM.

In SDK11.0, configured I2C2 to fast mode with wrong value also.

root@am62xx-evm:~# devmem2 0x200000b4

/dev/mem opened.

Memory mapped at address 0xffffa9bb3000.

Read at address 0x200000B4 (0xffffa9bb30b4): 0x00000009

root@am62xx-evm:~# devmem2 0x200100b4

/dev/mem opened.

Memory mapped at address 0xffff89f3d000.

Read at address 0x200100B4 (0xffff89f3d0b4): 0x0000000D

root@am62xx-evm:~# devmem2 0x200200b4

/dev/mem opened.

Memory mapped at address 0xffffbef3a000.

Read at address 0x200200B4 (0xffffbef3a0b4): 0x00000009

root@am62xx-evm:~#

root@am62xx-evm:~# devmem2 0x200000b8

/dev/mem opened.

Memory mapped at address 0xffffb340d000.

Read at address 0x200000B8 (0xffffb340d0b8): 0x00000003

root@am62xx-evm:~# devmem2 0x200100b8

/dev/mem opened.

Memory mapped at address 0xffff840d5000.

Read at address 0x200100B8 (0xffff840d50b8): 0x0000000F

root@am62xx-evm:~# devmem2 0x200200b8

/dev/mem opened.

Memory mapped at address 0xffffb30b8000.

Read at address 0x200200B8 (0xffffb30b80b8): 0x00000003

root@am62xx-evm:~#