Tool/software:

Here I am doing a LPDDR4 (3733Mbps) SI Simulation using Hyperlynx,

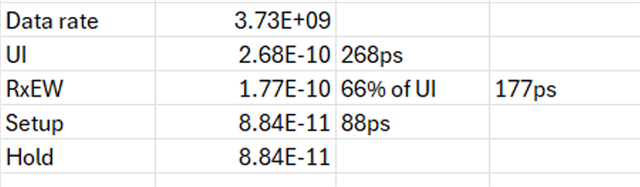

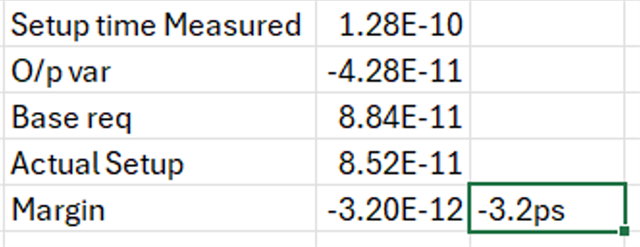

- In Read cycle we are failing with setup and hold time with the lesser margin.

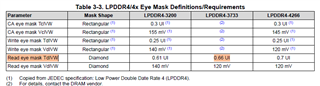

- Currently we are using Rx eye width =0.66UI (177ps) - As per the App note "LPDDR4_Board_design_and_layout_guidelines_spracn9e"

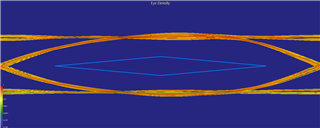

- The 0.66 UI seems to be very strict Eye mask and so Measurement tool shows a marginal failure even when we have considerable eye opening.

- Is there any updated specification for this Data rate if so please do send us..

App Note Snip

LPDDR4_Board_design_and_layout_guidelines_spracn9e.pdf

App Note File

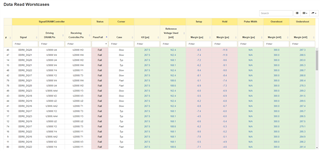

- This is the results of the Read Cycle from the DDR Batch report hyperlynx.