Tool/software:

When bringing up a SubDevice, the EtherCAT Master reads the content of the "emulated EEPROM" via the SubDevice Information Interface (SII). This involves writing the SII command interface registers starting at 0x0500, waiting for the SubDevice to clear the busy bit in register 0x0502, and then reading back the requested data word.

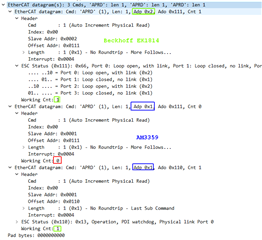

In some cases, we encounter a timeout when reading the SII. Our device has a Sitara 3359 and runs the Beckhoff Ethercat Slave Stack Code (SSC) 5.13 and TI PRU-ICSS-ETHERCAT-SLAVE 01_00_10_00. The MainDevice runs SOEM.

Attached is a Wireshark trace. The device in question has configured physical address 0xb. Use e.g. display filter eth.src contains 02:01 and ecat.ado eq 0x502.

At packet 19266, the MainDevice requests to read word 0x031a, but the busy bit stays on for at about 170ms, at which point the MainDevice gives up and reports a timeout. In contrast, other reads take less than a ms. The issue occurs every few boots.

We'd be grateful for any hints on how to further debug this. In particular, we are wondering where the reset of the busy bit happens: In the SSC or in the PRU firmware? And what triggers the reset?