Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

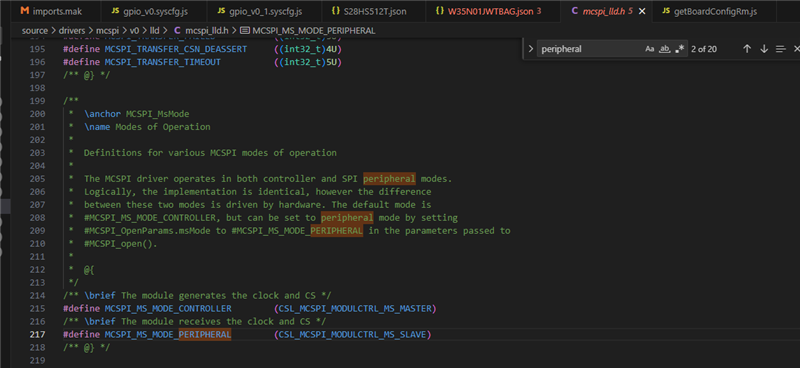

Hi, I 'am implementing a SPI Single Slave and now I want to know if chip select (CS) is used in polled mode. As far as I can tell, everything is still working when I disconnect CS (so i suspect its not used).

So my questions are:

Is CS used in polled mode?

Is callback interrupt mode working as Polled with regards to CS?