Other Parts Discussed in Thread: DRA821, TDA4VH

Tool/software:

Hi Ti

I use DRA821U evm (J7200) , SDK version:10_01_08_01

I can enabled USB3 function in kernel space and I it work. But same setting in uboot do not work.

U-boot log:

U-Boot SPL 2024.04-gb40fba1b-dirty (May 05 2025 - 11:31:08 +0800)

SYSFW ABI: 4.0 (firmware rev 0x000a '10.0.8--v10.00.08 (Fiery Fox)')

Trying to boot from MMC2

Warning: Detected image signing certificate on GP device. Skipping certificate to prevent boot failure. This will fail if the image was also encrypted

Warning: Detected image signing certificate on GP device. Skipping certificate to prevent boot failure. This will fail if the image was also encrypted

Warning: Detected image signing certificate on GP device. Skipping certificate to prevent boot failure. This will fail if the image was also encrypted

Warning: Detected image signing certificate on GP device. Skipping certificate to prevent boot failure. This will fail if the image was also encrypted

Warning: Detected image signing certificate on GP device. Skipping certificate to prevent boot failure. This will fail if the image was also encrypted

Loading Environment from nowhere... OK

Starting ATF on ARM64 core...

NOTICE: BL31: v2.10.0(release):b40fba1b-dirty

NOTICE: BL31: Built : 15:53:26, May 7 2025

I/TC:

I/TC: Primary CPU initializing

I/TC: SYSFW ABI: 4.0 (firmware rev 0x000a '10.0.8--v10.00.08 (Fiery Fox)')

I/TC: HUK Initialized

I/TC: Activated SA2UL device

I/TC: Fixing SA2UL firewall owner for GP device

I/TC: Enabled firewalls for SA2UL TRNG device

I/TC: SA2UL TRNG initialized

I/TC: SA2UL Drivers initialized

I/TC: Primary CPU switching to normal world boot

U-Boot SPL 2024.04-gb40fba1b-dirty (May 07 2025 - 15:54:37 +0800)

SYSFW ABI: 4.0 (firmware rev 0x000a '10.0.8--v10.00.08 (Fiery Fox)')

Detected: J7X-BASE-CPB rev A

Detected: J7X-GESI-EXP rev E3

Trying to boot from MMC2

Warning: Detected image signing certificate on GP device. Skipping certificate to prevent boot failure. This will fail if the image was also encrypted

Warning: Detected image signing certificate on GP device. Skipping certificate to prevent boot failure. This will fail if the image was also encrypted

U-Boot 2024.04-gb40fba1b-dirty (May 07 2025 - 15:54:37 +0800)

SoC: J7200 SR1.0 GP

Model: Texas Instruments J7200 EVM

Board: J7200X-PM2-SOM rev E6

DRAM: 2 GiB (effective 4 GiB)

Core: 114 devices, 32 uclasses, devicetree: separate

Flash: 0 Bytes

MMC: mmc@4f80000: 0, mmc@4fb0000: 1

Loading Environment from SPIFlash... k3-navss-ringacc ringacc@2b800000: Ring Accelerator probed rings:286, gp-rings[96,32] sci-dev-id:235

k3-navss-ringacc ringacc@2b800000: dma-ring-reset-quirk: disabled

jedec_spi_nor flash@0: non-uniform erase sector maps are not supported yet.

SF: Detected s28hs512t with page size 256 Bytes, erase size 4 KiB, total 64 MiB

*** Warning - bad CRC, using default environment

In: serial@2800000

Out: serial@2800000

Err: serial@2800000

am65_cpsw_nuss ethernet@46000000: K3 CPSW: nuss_ver: 0x6BA02102 cpsw_ver: 0x6BA82102 ale_ver: 0x00293904 Ports:1

Detected: J7X-BASE-CPB rev A

Detected: J7X-GESI-EXP rev E3

Net: eth0: ethernet@46000000port@1

Hit any key to stop autoboot: 0

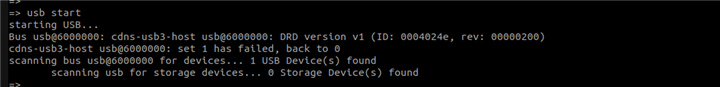

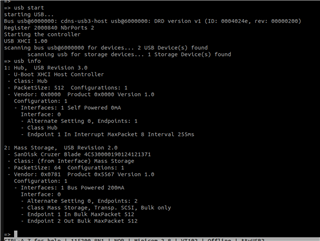

=> usb start

starting USB...

No working controllers found