Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

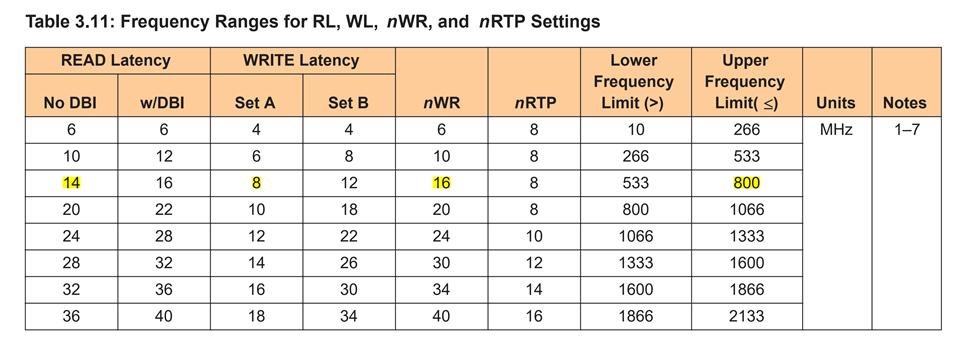

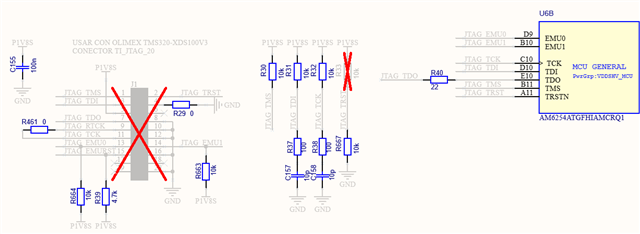

We have developed a custom board based on the AM6254ATGFHI, featuring an LPDDR4 memory interface using the ISSI IS43LQ16512A-053BLI device. All power rails for the various components are properly supplied, and the system reset signal is generated correctly. We are able to boot U-Boot from an SD card without issues.

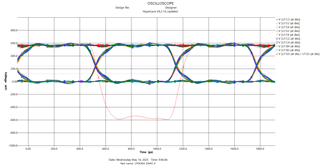

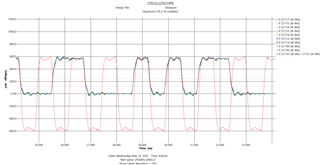

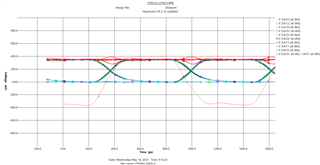

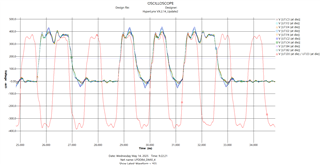

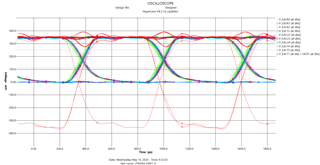

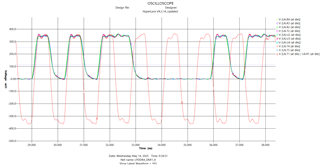

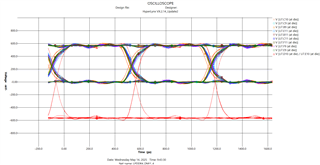

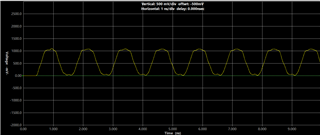

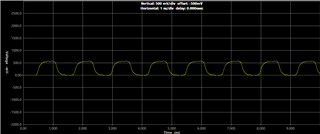

The LPDDR4 memory interface was simulated using HyperLynx, and the "DDRx Batch Simulation" passed successfully.

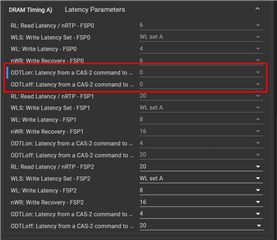

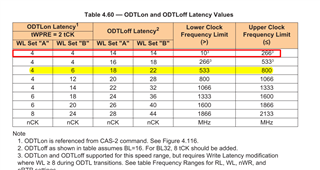

To generate the U-Boot configuration files, we used the TI SysConfig tool to create the DTSI file, based on the information provided in the memory device datasheet and the output of the signal integrity simulations.

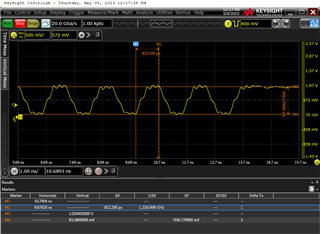

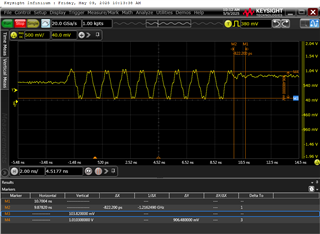

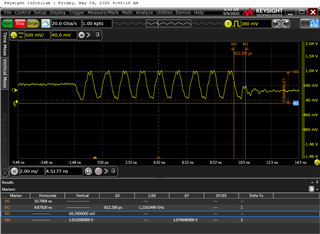

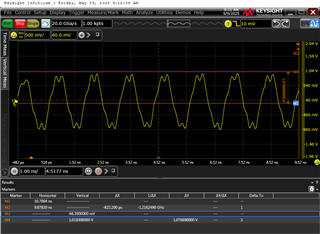

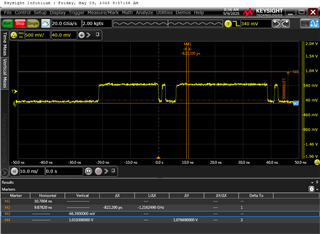

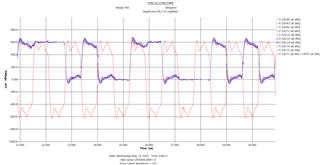

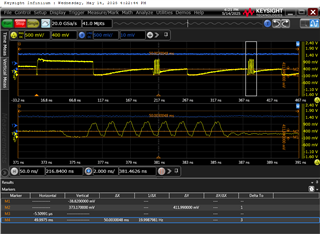

However, when booting the board and running a memory test, we observe frequent read/write errors where data appears as all zeros, instead of the expected values.

Could you provide any guidance on what we might be doing incorrectly?

Best regards.report_data.zipsettings_info_2505071627.zipSerial output UART0.txt