Part Number: PROCESSOR-SDK-AM62X

Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi Expert,

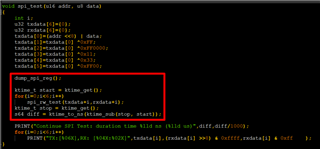

I use the following simple program snippet to illustrate our needs.

We hope to shorten the read and write time as much as possible.

Our interrupt program is executed every 125us. Each time it enters,

it needs to execute 6 SPI reads and writes twice.

The following is the time required to simulate a cycle.

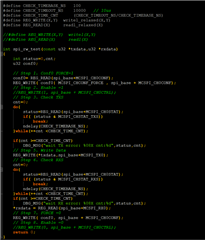

The following shows the dump of related registers before each execution of work, and the calculation of the time consumed.

The following is the program for reading and writing SPI.

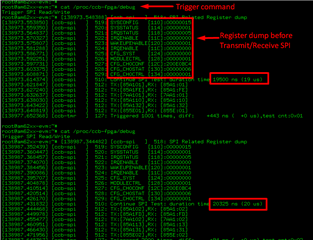

The time displayed on the oscilloscope is using writel/readl.

After that, using writel_relaxed/readl_relaxed can shorten some time, such as the time displayed on the console.

The following is the execution result displayed in the Console

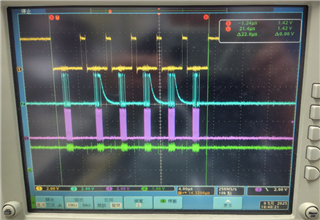

The following is the result displayed by the oscilloscope. (CLOCK=25MHz, DATA=24 bits)

We guess that if the control of CS can be not written to the FORCE bit through software, it may be possible to shorten some time.

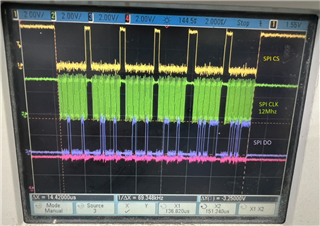

The following is the result of the test on our existing Cavium platform.(CLOCK=12MHz,DATA= 24bits)

We can see that the difference is that there is no redundant CS.

I am not sure whether waiting for TXS/RXS from CH0STAT is much greater than the actual transmission delay.

Thanks

Daniel