Tool/software:

Hi Expert,

We have 2 TDM streams connected to two McASP interfaces, each stream with 32 Tx & 32 Rx timeslots, each timeslot is 8 bits (A or Mu law),

and the operation mode is Slave Mode, so FS/CLK are input (from FPGA), there are 64 transmit and 64 receive channels to be processed.

In the McASP interface, we hope to design it into ping-pong mode, as follows:

- There is an independent continuous storage space for each TX and RX timeslot

2. Each buffer space can store 20ms of data (160 bytes), and the data is processed every 10ms (80 bytes)

3. These data can be automatically moved to the corresponding area through DMA

4. The application layer software can write or read the specified channel data every 10ms depending on the demand

Our questions are:

1. Is the above design requirement possible? Are there any known bottlenecks, such as DMA Quantity, space or time limitations, etc.

2. Is there a better or faster design than the above?

3. Is there a similar reference example ? (DTS, driver, DMA control...)

Hardware information as following:

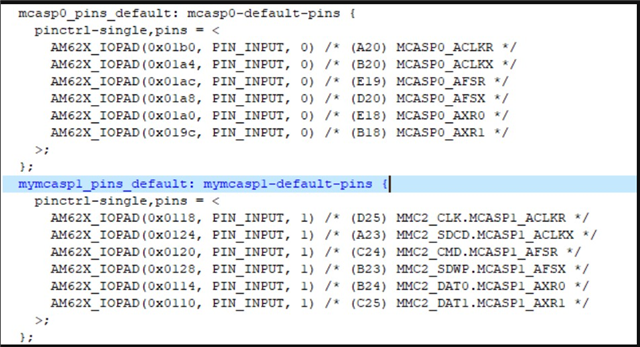

MCASP0_ACLKR=MCASP0_ACLKX=MCASP1_ACLKR=MCASP1_ACLKX <==FPGA CLK =2MHz

MCASP0_AFSR=MCASP0_AFSX=MCASP1_AFSR=MCASP1_AFSX <==FPGA FS = 8KHz

MCASP0_AXR0 ==>FPGA Stream 0 RX

MCASP0_AXR1 <==FPGA Stream 0 TX

MCASP1_AXR0 ==> FPGA Stream 1 RX

MCASP1_AXR1 <== FPGA Stream 1 TX

TDM stream:

FS : 8K

CLK: 2MHz

Thanks

Daniel