Tool/software:

Hi Experts,

Good day.

From the technical manual of AM335X:

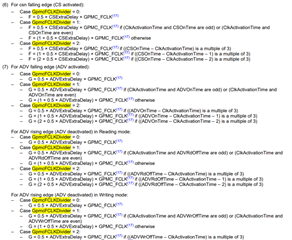

p128 only indicates cases 0, 1, and 2 for GpmcFCLKDivider:

Question: What would happen if its 3? Any equations?

Thank you.

Regards,

Archie A.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi Experts,

Good day.

From the technical manual of AM335X:

p128 only indicates cases 0, 1, and 2 for GpmcFCLKDivider:

Question: What would happen if its 3? Any equations?

Thank you.

Regards,

Archie A.

Hi Archie,

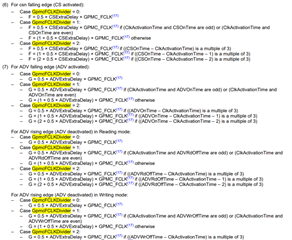

Not sure why they didn't extend the documentation to divide-by-4. GPMCFCLKDIVIDER does have a divide-by-4 option (0x3).

The only reason I can come up with is that ClkActivationTime only supports up to 2 GPMC_FCLK cycles after start access time, so the divide-by-4 mode get more restrictive than the others.

The notes you attached also don't address the use of TimeParaGranularty but I think that would double delays of the OnTime/OffTime counters.

What the notes are trying to enforce is the alignment of control signal transitions to the rise edge of the divided clock. GPMC wont enforce this for you - the signals transition on whichever FCLK cycle programmed in the respective OnTime/OffTime bit field.

GpmcFCLKDivider

Divides the GPMC_FCLK clock

0x0: GPMC_CLK frequency = GPMC_FCLK frequency

0x1: GPMC_CLK frequency = GPMC_FCLK frequency / 2

0x2: GPMC_CLK frequency = GPMC_FCLK frequency / 3

0x3: GPMC_CLK frequency = GPMC_FCLK frequency /4

ClkActivationTime

Output GPMC_CLK activation time

0x0: First rising edge of GPMC_CLK at start access time

0x1: First rising edge of GPMC_CLK one GPMC_FCLK cycle after start access time

0x2: First rising edge of GPMC_CLK two GPMC_FCLK cycles after start access time

0x3: Reserved

Regards,

Mark