Tool/software:

Dear TIs.

I need to implement the PCIe interface between the AM6442 microcontroller and the FPGA, where the AM6442 serves as the RC mode. Now the AM6442 and FPGA have established a link. The FPGA prompts for link establishment, and the LTSSM on the AM6442 side has also entered state L0. After the program runs, can I modify the data of the local address of the outbound through the Memory browser of CCS to modify the data of the corresponding address of the PCIe bus?

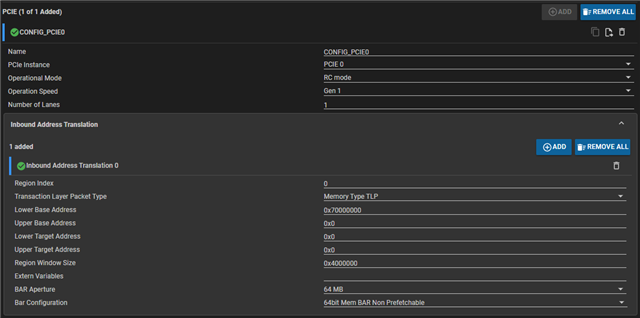

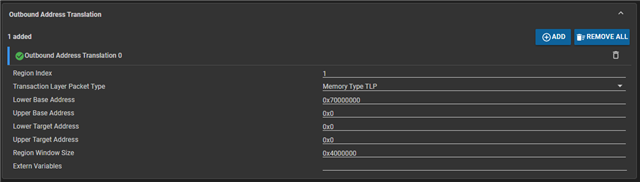

Below is the configuration of the PCIe interface in my SysCfg file.

May I ask if there is any problem with my configuration file? What aspects should be noted for the consistency with the FPGA side?

The official SDK examples all use AM6442 as the EP end. Where can I get cases about using AM6442 as the RC end?

Thank you.