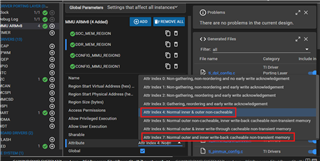

Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi,

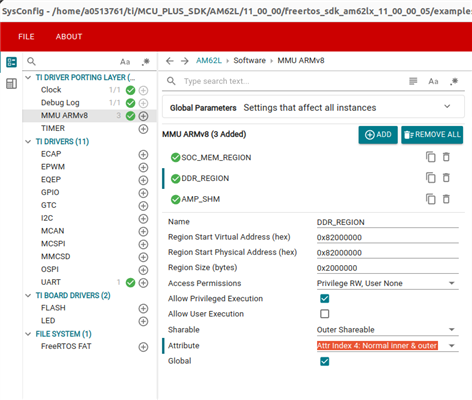

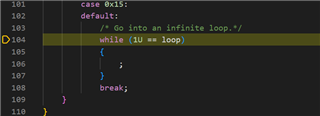

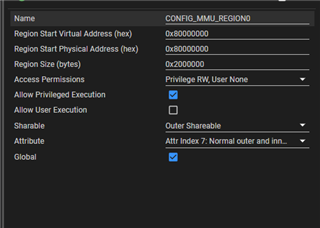

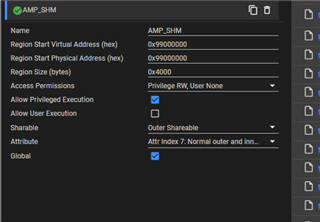

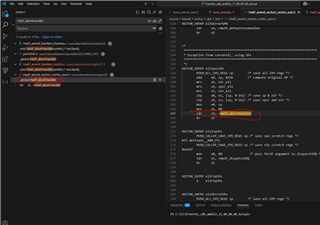

For HW validation, we would like to disable cache to make sure all data are raw and direct data. However, if I comment out the cache_enable under this function, whole application will not boot up. Is there a way to be in a cache-free environment?