Part Number: AM6442

Tool/software:

Hi Support Team,

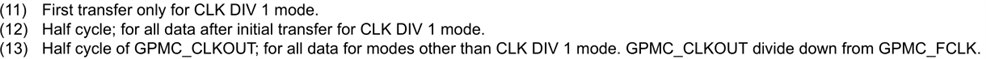

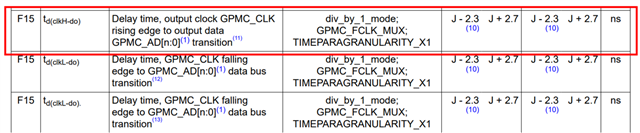

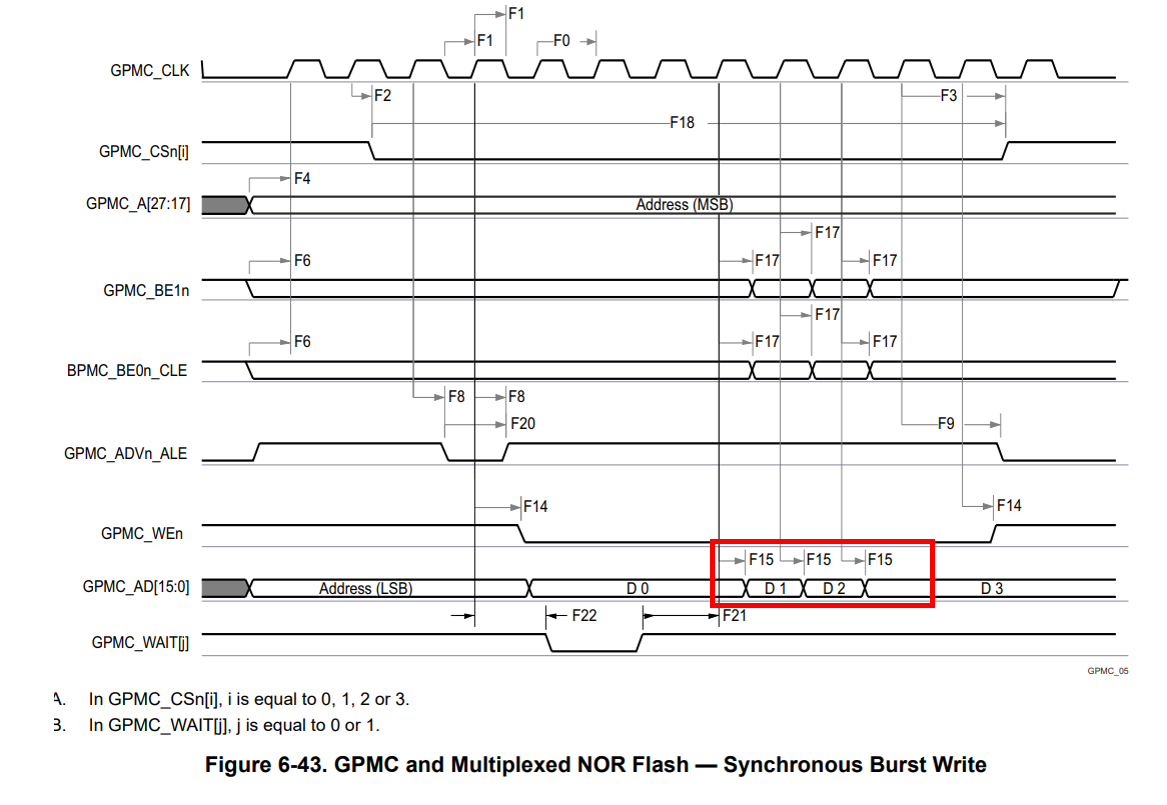

I would like to confirm the AM6442 datasheet: Table 6-55. GPMC and NOR Flash Switching Characteristics - Synchronous Mode.

My customer is developing a board with AM6442 and is trying to set timing restrictions (setup, hold) in FPGA.

In the above specification, J = GPMC_CLK, so at 50MHz, this would be 20ns.

In this case, Min = 17.7ns and Max = 22.7ns, so is it correct to expect the valid data width is between 17.7ns and 22.7ns?

Unlike other specifications, this one only specifies TRANSITION time, so let me check just to be sure.

Best Regards,

Kanae