Other Parts Discussed in Thread: AM62A7

Tool/software:

Hello TI Dev,

This is a basic custom model that I built on tensorflow/keras and convert it to tflite file. The model is non-image model.

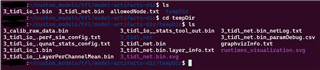

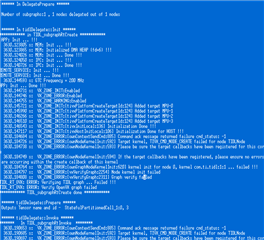

I copied tflite file to edgeai_tidl_tool directory inside ./model/public. I already provided model config in the github.com/.../model_configs.py however, I am not sure if I provide a correct model config. The model config is shown as follow.

Regards,

Key