Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hello everyone,

I am contacting you because I notice performance problems in my system.

To give some context, I work with the AM6642 EVM card in order to establish an EtherCAT communication with a slave network.

The performance of our system is quite critical with a cycle time around one hundred μs. We have to optimize everything so that everything happens as quickly as possible.

As such, our application uses DMA and PRU to interface with the Ethernet PHY which allows sending the EtherCAT frame.

My problem is the following: The time between when the frame arrives on the PHY of the AM6442 and when the frame is actually available in our application is abnormally long (it takes 15 μs for a frame of 800 bytes).

I would have thought that this time would be much shorter, about 2-3 μs. Our application is running on a R5F-cortex (MAIN_Cortex_R5_0_0).

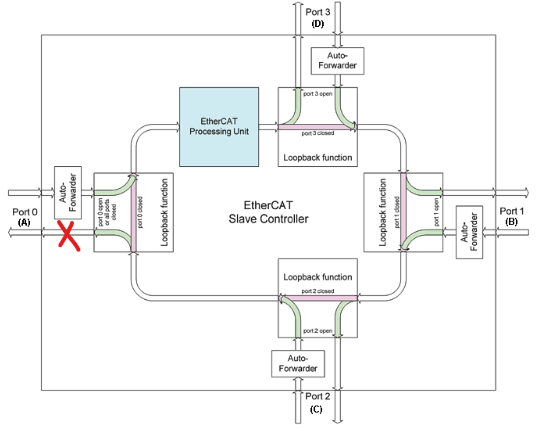

If I understand correctly, the frame arrives on the Ethernet port, the PRU processes it in real time (so we hope that it takes very little time) and then gives the frame to the DMA which puts it in the desired memory space (in our application in MSRAM).

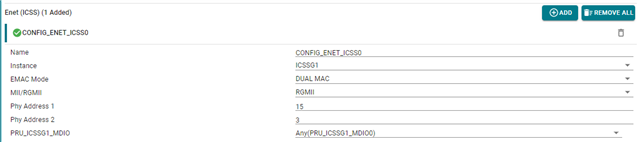

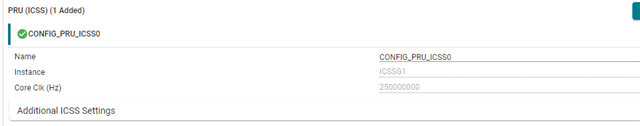

From what I understand, the DMA is well used and we configure the PRU in the sysconfig as follows:

I am aware of not giving much information but I do not know what to provide.

Do you know how I can reduce this time? Is it possible to reduce it significantly? Do you have any idea how long this could take?

Don’t hesitate to let me know if you need information.

Thank you very much for your help.

Maxime.