Tool/software:

Hi TI supporters,

I have a custom board based on J721S2 (TDA4AL) with two PHYs connected:

- MCU_CPSW: TI DP83867 (good working and no problem)

- MAIN_CPSW: RTL9010ARG

In u-boot (2023.04), the RTL9010ARG is properly recognized through MDIO and PHY initialization is performed successfully (see logs below).

However, in QNX 7.1, the RTL9010ARG PHY is not communicating properly through MDIO.

I would appreciate it if you could help identify the reason why communication is not working.

hw_init.c BSP source file

#define EVM_CPSW_MCU_RGMII_INT_PIN_NUM (3U)

#define EVM_CPSW_MCU_RGMII_RST_PIN_NUM (56U)

//#define EVM_CPSW_RGMII_INT_PIN_NUM (23U)

#define EVM_CPSW_RGMII_INT_PIN_NUM (20U)

static int init_cpsw2g(void)

{

kprintf("MAIN_CPSW, RTL9010ARG Phy init..\n");

/**** MAIN_CPSW ****/

/* MDIO 0 */

out32(J721S2_CTRLMMR_PADCONFIG + PIN_MCASP1_AXR0, PIN_PULL_DISABLE | PIN_MODE(6)); /* MCASP1_AXR0.MDIO0_MDC (T28) */

out32(J721S2_CTRLMMR_PADCONFIG + PIN_MCASP1_AFSX, PIN_INPUT_ENABLE | PIN_PULL_DISABLE | PIN_MODE(6)); /* MCASP1_AFSX.MDIO0_MDIO (V28) */

/* RGMII1 */

out32(J721S2_CTRLMMR_PADCONFIG + PIN_MCASP1_ACLKX, PIN_INPUT_ENABLE | PIN_PULL_DISABLE | PIN_MODE(6)); /* MCASP1_ACLKX.RGMII1_RD0 (AA24) */

out32(J721S2_CTRLMMR_PADCONFIG + PIN_MCASP0_AXR12, PIN_INPUT_ENABLE | PIN_PULL_DISABLE | PIN_MODE(6)); /* MCASP0_AXR12.RGMII1_RD1 (AB25) */

out32(J721S2_CTRLMMR_PADCONFIG + PIN_MCASP0_AXR13, PIN_INPUT_ENABLE | PIN_PULL_DISABLE | PIN_MODE(6)); /* MCASP0_AXR13.RGMII1_RD2 (T23) */

out32(J721S2_CTRLMMR_PADCONFIG + PIN_MCASP0_AXR14, PIN_INPUT_ENABLE | PIN_PULL_DISABLE | PIN_MODE(6)); /* MCASP0_AXR14.RGMII1_RD3 (U24) */

out32(J721S2_CTRLMMR_PADCONFIG + PIN_MCASP1_AXR3, PIN_INPUT_ENABLE | PIN_PULL_DISABLE | PIN_MODE(6)); /* MCASP1_AXR3.RGMII1_RXC (AD26) */

out32(J721S2_CTRLMMR_PADCONFIG + PIN_MCASP0_AXR15, PIN_INPUT_ENABLE | PIN_PULL_DISABLE | PIN_MODE(6)); /* MCASP0_AXR15.RGMII1_RX_CTL (AC25) */

out32(J721S2_CTRLMMR_PADCONFIG + PIN_MCASP0_AXR7, PIN_PULL_DISABLE | PIN_MODE(6)); /* MCASP0_AXR7.RGMII1_TD0 (T25) */

out32(J721S2_CTRLMMR_PADCONFIG + PIN_MCASP0_AXR8, PIN_PULL_DISABLE | PIN_MODE(6)); /* MCASP0_AXR8.RGMII1_TD1 (W24) */

out32(J721S2_CTRLMMR_PADCONFIG + PIN_MCASP0_AXR9, PIN_PULL_DISABLE | PIN_MODE(6)); /* MCASP0_AXR9.RGMII1_TD2 (AA25) */

out32(J721S2_CTRLMMR_PADCONFIG + PIN_MCASP0_AXR10, PIN_PULL_DISABLE | PIN_MODE(6)); /* MCASP0_AXR10.RGMII1_TD3 (V25) */

out32(J721S2_CTRLMMR_PADCONFIG + PIN_MCASP1_AXR4, PIN_PULL_DISABLE | PIN_MODE(6)); /* MCASP1_AXR4.RGMII1_TXC (U25) */

out32(J721S2_CTRLMMR_PADCONFIG + PIN_MCASP0_AXR11, PIN_PULL_DISABLE | PIN_MODE(6)); /* MCASP0_AXR11.RGMII1_TX_CTL (T24) */

// GPIO0_23 as Interrupt

//out32(J721S2_CTRLMMR_PADCONFIG + PIN_MCASP2_AXR0, PIN_INPUT_ENABLE | PIN_PULL_DISABLE | PIN_MODE(7));

// GPIO0_20 (W27)

out32(J721S2_CTRLMMR_PADCONFIG + PIN_MCASP1_AXR2, PIN_INPUT_ENABLE | PIN_PULL_DISABLE | PIN_MODE(7));

//GPIO0_20 as input

out32(J721S2_GPIO0_BASE + J721S2_GPIO_DIR(EVM_CPSW_RGMII_INT_PIN_NUM),

in32(J721S2_GPIO0_BASE + J721S2_GPIO_DIR(EVM_CPSW_RGMII_INT_PIN_NUM)) | (J721S2_GPIO_BIT(EVM_CPSW_RGMII_INT_PIN_NUM)));

// Default signal voltage 3.3v, output low

out32(J721S2_GPIO0_BASE + J721S2_GPIO_CLR_DATA(EVM_CPSW_RGMII_INT_PIN_NUM), (unsigned int)(J721S2_GPIO_BIT(EVM_CPSW_RGMII_INT_PIN_NUM)));

/**** MCU_CPSW ****/

/* MDIO 0 */

out32(J721S2_WKUP_CTRLMMR_PADCONFIG + PIN_MCU_MDIO0_MDC, PIN_PULL_DISABLE | PIN_MODE(0)); /* MCU MDIO0_MDC */

out32(J721S2_WKUP_CTRLMMR_PADCONFIG + PIN_MCU_MDIO0_MDIO, PIN_INPUT_ENABLE | PIN_PULL_DISABLE | PIN_MODE(0)); /* MCU MDIO0_MDIO */

/* MCU_RGMII1 */

out32(J721S2_WKUP_CTRLMMR_PADCONFIG + PIN_MCU_RGMII1_RD0, PIN_INPUT_ENABLE | PIN_PULL_DISABLE | PIN_MODE(0)); /* MCU RGMII1_RD0 */

out32(J721S2_WKUP_CTRLMMR_PADCONFIG + PIN_MCU_RGMII1_RD1, PIN_INPUT_ENABLE | PIN_PULL_DISABLE | PIN_MODE(0)); /* MCU RGMII1_RD1 */

out32(J721S2_WKUP_CTRLMMR_PADCONFIG + PIN_MCU_RGMII1_RD2, PIN_INPUT_ENABLE | PIN_PULL_DISABLE | PIN_MODE(0)); /* MCU RGMII1_RD2 */

out32(J721S2_WKUP_CTRLMMR_PADCONFIG + PIN_MCU_RGMII1_RD3, PIN_INPUT_ENABLE | PIN_PULL_DISABLE | PIN_MODE(0)); /* MCU RGMII1_RD3 */

out32(J721S2_WKUP_CTRLMMR_PADCONFIG + PIN_MCU_RGMII1_RXC, PIN_INPUT_ENABLE | PIN_PULL_DISABLE | PIN_MODE(0)); /* MCU RGMII1_RXC */

out32(J721S2_WKUP_CTRLMMR_PADCONFIG + PIN_MCU_RGMII1_RX_CTL, PIN_INPUT_ENABLE | PIN_PULL_DISABLE | PIN_MODE(0)); /* MCU RGMII1_RX_CTL */

out32(J721S2_WKUP_CTRLMMR_PADCONFIG + PIN_MCU_RGMII1_TD0, PIN_PULL_DISABLE | PIN_MODE(0)); /* MCU RGMII1_TD0 */

out32(J721S2_WKUP_CTRLMMR_PADCONFIG + PIN_MCU_RGMII1_TD1, PIN_PULL_DISABLE | PIN_MODE(0)); /* MCU RGMII1_TD1 */

out32(J721S2_WKUP_CTRLMMR_PADCONFIG + PIN_MCU_RGMII1_TD2, PIN_PULL_DISABLE | PIN_MODE(0)); /* MCU RGMII1_TD2 */

out32(J721S2_WKUP_CTRLMMR_PADCONFIG + PIN_MCU_RGMII1_TD3, PIN_PULL_DISABLE | PIN_MODE(0)); /* MCU RGMII1_TD3 */

out32(J721S2_WKUP_CTRLMMR_PADCONFIG + PIN_MCU_RGMII1_TXC, PIN_PULL_DISABLE | PIN_MODE(0)); /* MCU RGMII1_TXC */

out32(J721S2_WKUP_CTRLMMR_PADCONFIG + PIN_MCU_RGMII1_TX_CTL, PIN_PULL_DISABLE | PIN_MODE(0)); /* MCU RGMII1_TX_CTL */

// WKUP_GPIO0_3 as Interrupt

out32(J721S2_WKUP_CTRLMMR_PADCONFIG + PIN_WKUP_GPIO0_3, PIN_INPUT_ENABLE | PIN_PULL_DISABLE | PIN_MODE(7));

// WKUP_GPIO0_3 as input

out32(J721S2_WKUP_GPIO0 + J721S2_GPIO_DIR(EVM_CPSW_MCU_RGMII_INT_PIN_NUM),

in32(J721S2_WKUP_GPIO0 + J721S2_GPIO_DIR(EVM_CPSW_MCU_RGMII_INT_PIN_NUM)) | (J721S2_GPIO_BIT(EVM_CPSW_MCU_RGMII_INT_PIN_NUM)));

// Default signal voltage 3.3v, output low

out32(J721S2_WKUP_GPIO0 + J721S2_GPIO_CLR_DATA(EVM_CPSW_MCU_RGMII_INT_PIN_NUM), (unsigned int)(J721S2_GPIO_BIT(EVM_CPSW_MCU_RGMII_INT_PIN_NUM)));

// WKUP_GPIO0_56 as Reset

out32(J721S2_WKUP_CTRLMMR_PADCONFIG + PIN_WKUP_GPIO0_56, PIN_OUTPUT_DISABLE | PIN_PULL_DISABLE | PIN_MODE(7));

// WKUP_GPIO0_56 as Output

out32(J721S2_WKUP_GPIO0 + J721S2_GPIO_DIR(EVM_CPSW_MCU_RGMII_RST_PIN_NUM),

in32(J721S2_WKUP_GPIO0 + J721S2_GPIO_DIR(EVM_CPSW_MCU_RGMII_RST_PIN_NUM)) & ~(J721S2_GPIO_BIT(EVM_CPSW_MCU_RGMII_RST_PIN_NUM)));

// Default signal voltage 3.3v, output high

out32(J721S2_WKUP_GPIO0 + J721S2_GPIO_SET_DATA(EVM_CPSW_MCU_RGMII_INT_PIN_NUM), (unsigned int)(J721S2_GPIO_BIT(EVM_CPSW_MCU_RGMII_INT_PIN_NUM)));

/* Power on CPSW1 module. */

if (ti_sci_set_device_state(TISCI_DEV_CPSW1, 0, MSG_DEVICE_SW_STATE_ON) == -1) {

kprintf("%s: Set CPSW1 device state failed!\n", __func__);

return -1;

}

return 0;

}

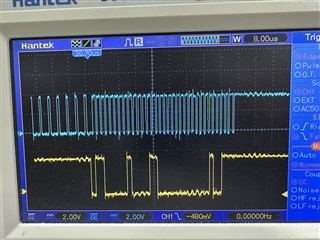

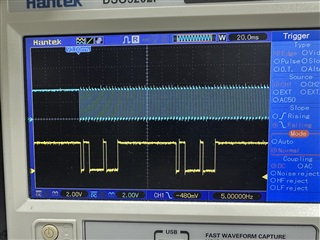

Boot and Debug Logs

The boot and debug logs are as follows: