Part Number: TDA4VH-Q1

Tool/software:

Hi Team,

I tried to give below commands to generate keys & build keywriter binary after adding OTP addon into 10.1 PSDK:

./gen_keywr_cert.sh -t keys/ti_fek_public.pem -s keys/smpk.pem --smek keys/smek.key

make keywriter_img BOARD=j784s4_evm

Debug reponse -> 65536

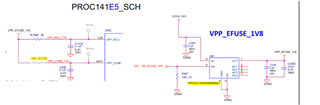

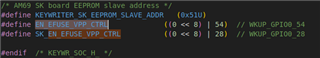

Found ouput 1V8 is not coming to VPP pins used below reference from TI: [working on why output is not coming as expected]

Using WKUP_GPIO_28 from keywriter application.

Using WKUP_GPIO_28 from keywriter application.

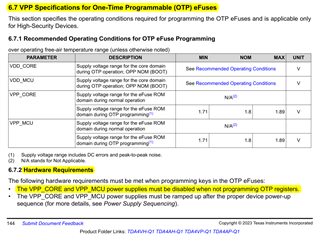

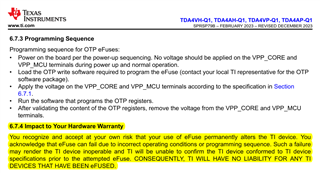

Question: Can we give directly 1.8V to VPP_MCU & VPP_CORE pins?

Thanks,

Sriram