Other Parts Discussed in Thread: TDA4VH

Tool/software:

Hi expers,

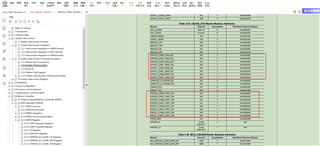

On TDA4VH, are those QOS of R5 configurable? I know VM is configurable, but all these registers on VH read 0.

Note: The reason I do this is because we have a problem on our side: When we turn on the display function, the spi interrupt processing time increases by one half, which causes the spi related functions of R5 core to be abnormal, so we try to modify the QOS to enhance the interrupt processing speed of R5 core. If you have other solutions to this problem or can reduce the spi interrupt processing time, please let us know.