Other Parts Discussed in Thread: DRA821, J721EXCPXEVM

Tool/software:

Hi Team,

Hardware Setup

- **Board**: J7200-EVM with DRA821 SoC

- **OS**: Yocto-built Linux image (Kernel 6.1.80-ti-g2e423244f8c0)

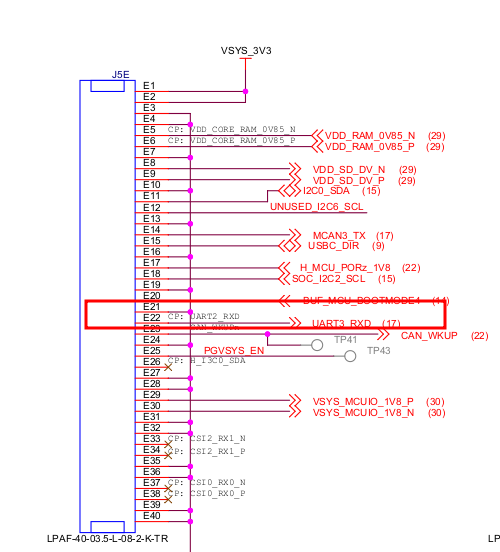

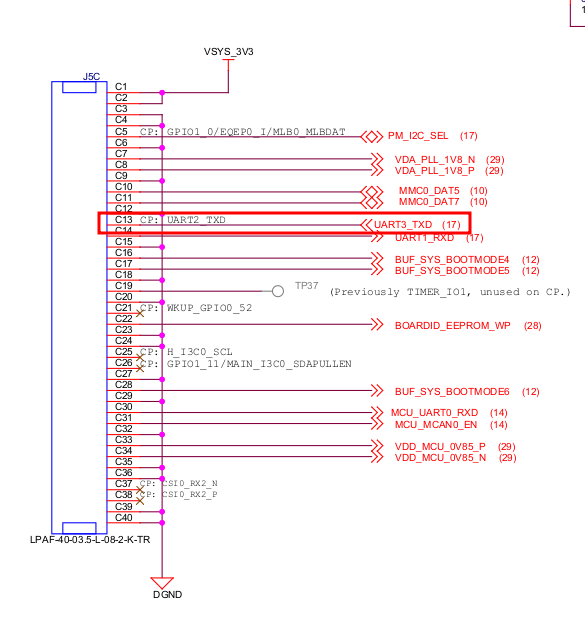

- **Target**: Configure UART0/UART1 for GNSS data reception

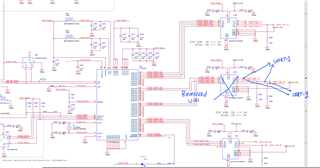

- **Multiplexer**: SN74CB3Q3257PWR (U41) controlling UART/LIN selection

Goal -

I need to configure the multiplexer to route signals to UART (instead of LIN) to receive GNSS data from one of the UART ports (UART0 or UART1).

Current Status - What I've Achieved

1. Identified the Multiplexer Control GPIOs

Using `gpioinfo`, we found the control lines:

gpiochip0 - 8 lines:

line 4: "UART/LIN_MUX_SEL" unused input active-high

line 6: "GPIO_LIN_EN" unused input active-high

2. Successfully Reading GPIO Status

bash

# Current configuration shows UART mode

root@j7200-evm:~# gpioget gpiochip0 4 # UART/LIN_MUX_SEL = 0 (UART mode)

0

root@j7200-evm:~# gpioget gpiochip0 6 # GPIO_LIN_EN = 0 (LIN disabled)

0

3. Confirmed libgpiod Tools Are Available

bash

root@j7200-evm:~# which gpioget gpioset gpioinfo

/usr/bin/gpioget

/usr/bin/gpioset

/usr/bin/gpioinfo

4. Current Multiplexer Status

The multiplexer appears to be configured for **UART mode**:

- `UART/LIN_MUX_SEL = 0` → Signals routed to UART

- `GPIO_LIN_EN = 0` → LIN transceiver disabled

Questions and Issues

1. GPIO Control Behavior

When using `gpioset gpiochip0 4=0 6=0`, the command executes without error, but `gpioinfo` still shows the lines as "unused input". Is this expected behavior, or should they show as "output [used]"?

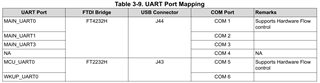

2. UART Device Availability

With the multiplexer configured for UART mode, what should be the expected device paths for UART0 and UART1? Should they appear as `/dev/ttyS0` and `/dev/ttyS1`, or different device nodes?

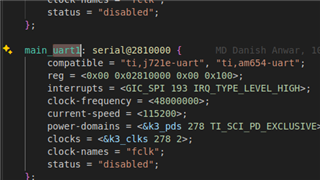

3. Device Tree Configuration

Should I check or modify any device tree settings to ensure UART0 and UART1 are properly enabled? The current boot args show:

console=ttyS2,115200n8 earlycon=ns16550a,mmio32,0x02800000

4. Persistent GPIO Configuration

Is there a recommended method to make the GPIO multiplexer configuration persistent across reboots? Should this be handled in the device tree, or through userspace scripts?

5. Hardware Validation

How can I verify that the multiplexer is actually switching the signals correctly? Are there any recommended testing procedures for the J7200-EVM UART/LIN functionality?

## Commands I've Used So Far

bash

# Check GPIO status

gpioinfo gpiochip0

gpioget gpiochip0 4 6

# Configure for UART mode

gpioset gpiochip0 4=0 6=0

# Configure for LIN mode (if needed)

gpioset gpiochip0 4=1 6=1

# Check available UART devices

ls -la /dev/ttyS*

Expected Next Steps

1. Confirm UART devices are available and accessible

2. Test UART communication with GNSS module

3. Validate signal routing through the multiplexer

4. Implement persistent configuration if needed

Request for Guidance

I would appreciate any insights on:

- Proper UART device configuration for J7200-EVM

- Best practices for multiplexer control on TI EVMs

- Device tree modifications (if any) required

- Testing procedures to validate UART/LIN switching

Hardware Details:

- SoC: DRA821 (J7200)

- Board: J7200-EVM

- Multiplexer: SN74CB3Q3257PWR (U41)

- I2C GPIO Expander: Address 0x21 on I2C bus 1