Other Parts Discussed in Thread: TDA4VL, SYSCONFIG

Tool/software:

Hi, Dear Expert

This is an extension discussion from this thread,

Because customer try to launch CCS debug with customized board for 1GB LPDDR4, and I saw this error message

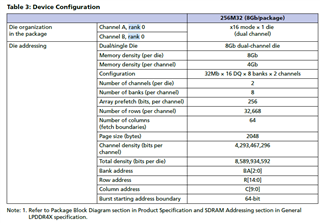

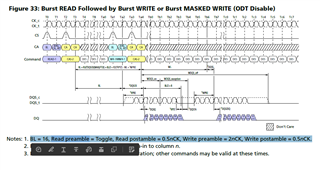

so I suspect it should be DDR initialize problems, post this thread for DDR setting double checking.

721S2 Running the DDR configuration... Wait till it completes! Error evaluating "J7_LPDDR4_Config_Late()": Target failed to read 0x80114080 at (*((unsigned int*) (0x80000000U+fsp_clkchng_req_addr))&0x80) [J7_DDR_Config.gel:3337] at DDRSS_LPDDR4_Ack_Freq_Upd_Req(ddrss_num) [J7_DDR_Config.gel:3413] at J7_LPDDR4_Config_Single(0) [J7_DDR_Config.gel:3699] at J7_LPDDR4_Config() [J7_DDR_Config.gel:3734] at J7_LPDDR4_Config_Late() (C:\src\0506\launch.js#130)

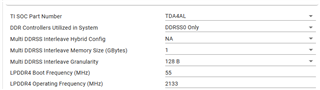

(1) Pls check basic setting, is it correct?

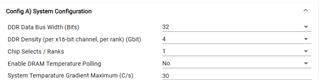

(2) plc check Config A, System Configuration, is it correct?

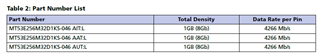

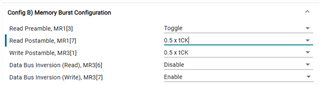

(3) Config B, Memory Burst Configuration, is it correct?

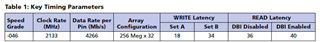

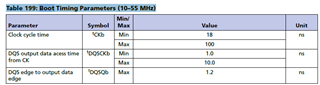

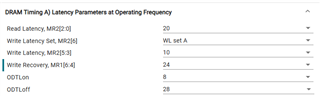

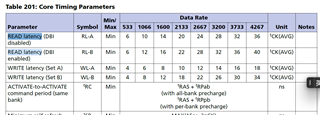

(4) DRAM Timing A) Latency Parameters at Operating Frequency, is it correct?

DDR sys configure as attachment

https://e2e.ti.com/cfs-file/__key/communityserver-discussions-components-files/791/tda4al_5F00_1g_5F00_ddr.syscfg

Thank You.

Gibbs