Tool/software:

Hi,

We are currently investigating a Linux boot issue on the AM4378, and I would like to ask for your clarification regarding the ECC configuration during NAND boot.

We are using a NAND device from Micron (MT29F8G08ABACAWP), which has a 2KB page size.

Upon reviewing the U-Boot documentation (doc/README.nand), we found a statement around line 260 indicating that BCH16 is not supported for NANDs with 2KB page sizes.

In light of this, we would like to confirm the following points:

-

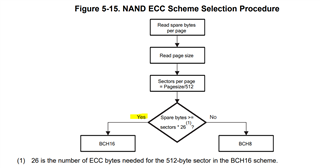

For a NAND device with a 2KB page size, should we strictly use BCH8 (instead of BCH16) as the ECC scheme?

-

During boot from NAND, when the AM4378 ROM reads the SPL (MLO), is BCH8 ECC used by default in the ROM code?

If there are any limitations or implementation notes we should be aware of, we would appreciate your guidance.

Thank you in advance for your support.

Best regards,

Conor