Part Number: DRA829J

Tool/software:

Dear TI-Team,

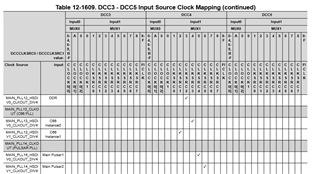

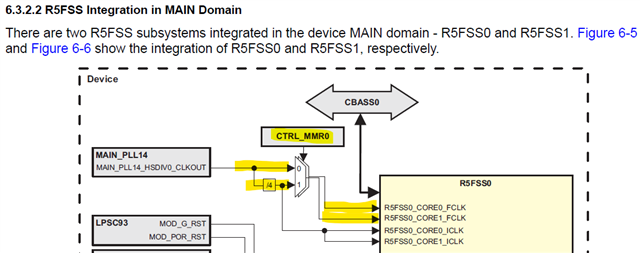

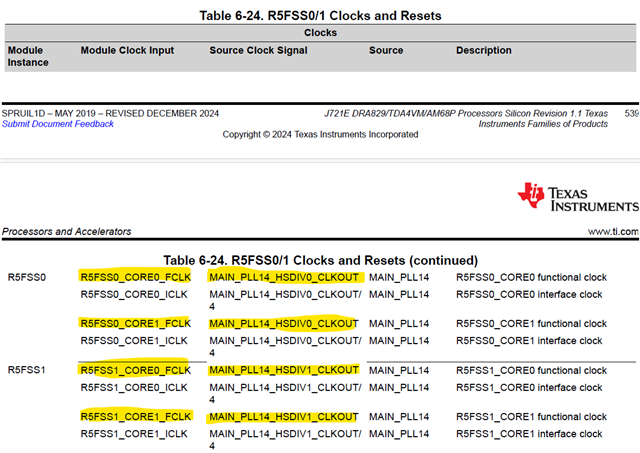

While checking the TRM for the functional clock sources of R5FSS0 and R5FSS1, we realized that in the integration diagram there's a CTRL_MMR0 register to select the clock source.

However, when checking the table with the corresponding options, there's only a single value. Also, we didn't find any register to select clock source for R5FSS0 and R5FSS1.

Either diagram is wrong or table needs to be updated. See pictures below:

Can you please check and confirm which is the correct information?

Thank you in advance.

Regards,

António