Tool/software:

Hi TI Support Team,

we use sdk 10.

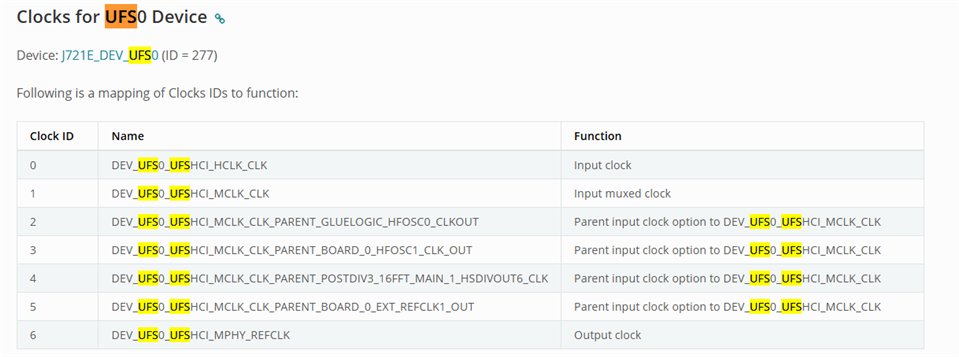

I’m working on a J721E (TDA4VM) and need to run the UFS controller’s MCLK at 26 MHz.

Using k3conf I see the relevant clock IDs:

root@j721e-evm:~# k3conf dump clock 277

|------------------------------------------------------------------------------|

| VERSION INFO |

|------------------------------------------------------------------------------|

| K3CONF | (version 0.3-nogit built Thu Jul 25 14:13:02 UTC 2024) |

| SoC | J721E SR1.1 |

| SYSFW | ABI: 4.0 (firmware version 0x000a '10.0.8--v10.00.08 (Fiery Fox))') |

|------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------------------------------------------------------|

| Device ID | Clock ID | Clock Name | Status | Clock Frequency |

|--------------------------------------------------------------------------------------------------------------------------------|

| 277 | 0 | DEV_UFS0_UFSHCI_HCLK_CLK | CLK_STATE_READY | 250000000 |

| 277 | 1 | DEV_UFS0_UFSHCI_MCLK_CLK | CLK_STATE_READY | 19200000 |

| 277 | 2 | DEV_UFS0_UFSHCI_MCLK_CLK_PARENT_GLUELOGIC_HFOSC0_CLKOUT | CLK_STATE_READY | 19200000 |

| 277 | 3 | DEV_UFS0_UFSHCI_MCLK_CLK_PARENT_BOARD_0_HFOSC1_CLK_OUT | CLK_STATE_READY | 0 |

| 277 | 4 | DEV_UFS0_UFSHCI_MCLK_CLK_PARENT_POSTDIV3_16FFT_MAIN_1_HSDIVOUT6_CLK | CLK_STATE_READY | 19200000 |

| 277 | 5 | DEV_UFS0_UFSHCI_MCLK_CLK_PARENT_BOARD_0_EXT_REFCLK1_OUT | CLK_STATE_READY | 0 |

| 277 | 6 | DEV_UFS0_UFSHCI_MPHY_REFCLK | CLK_STATE_READY | 0 |

|--------------------------------------------------------------------------------------------------------------------------------|

Goal

• Make ID 1 (MCLK) use parent ID 3 (HFOSC1/EXT_REFCLK1) at 26 MHz.