Tool/software:

Hello all,

I am running an test application for SPI Driver Version 9.0.1 on the R5 core of AM62A-LP SOC attached code and configuration

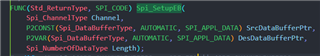

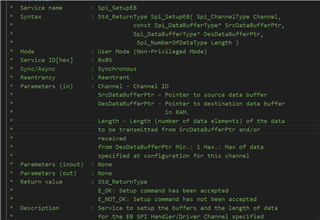

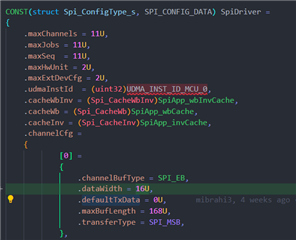

- Configuration:

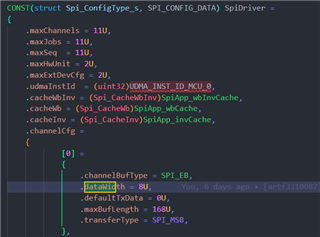

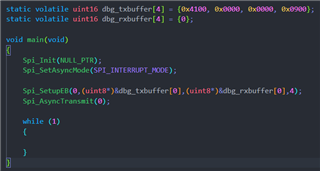

- Test Code:

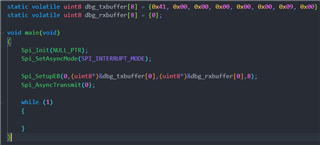

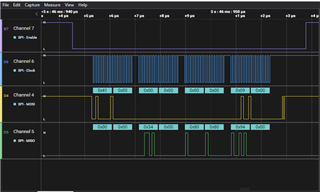

- Output on the SPI Bus:

-

dbg_rxbuffer values in the debugger: {0x00,0x00,0x34,0x00,0x80,0x80,0x94,0x00} Match the Data on the SPI BUS

The Issue is when I am changing the Data width to be 16 instead of 8 the value of the dbg_rxbuffer doesn't match the actual data on the SPI BUS.

Kindly check the modification for this part:

- Configuration:

- Test Code:

- Output on the SPI BUS:

-

dbg_rxbuffer values in the debugger: {0x0000, 0x3400, 0x3400, 0x3400} but this doesn't match what we could see on the SPI BUS.

Could you please support in this Issue.

Thanks in Advance