Tool/software:

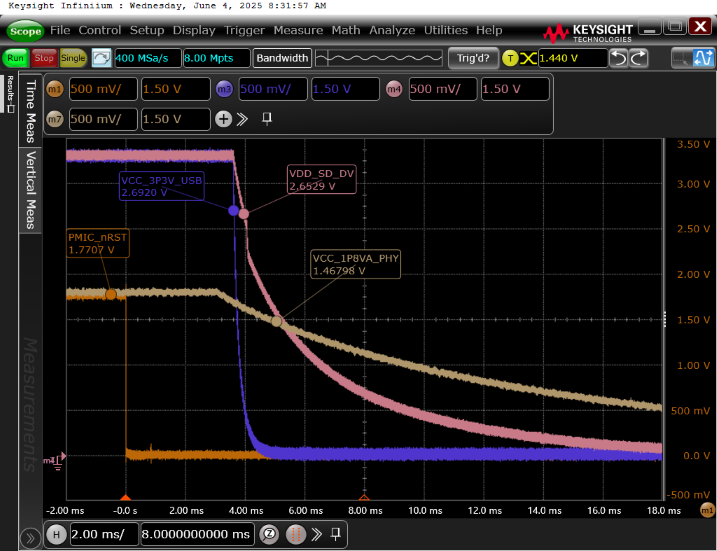

Section "6.10.2Power Supply Sequencing" in the datasheet describes various power supply sequences and specifies time stamps that indicate approximate elapsed times.

For example, section "6.10.2.2 Combined MCU and Main Domains Power-Up Sequencing" specifies time stamps as follows.

• T0 – 3.3V voltages start ramp-up to VOPR MIN. (0 ms)

• T1 – 1.8-V voltages start ramp-up to VOPR MIN. (2 ms)

• T2 – Low voltage core supplies start ramp-up to VOPR MIN. (3 ms)

• T3 – Low voltage RAM array voltages start ramp-up to VOPR MIN. (4 ms)

• T4 – OSC1 is stable and PORz/MCU_PORz are de-asserted to release processor from reset. (13 ms)

I understand that the time stamps are approximate and not strict timing requirements.

Can the times indicated by the time stamps be ignored?

Best regards,

Daisuke