Other Parts Discussed in Thread: AM62L

Tool/software:

Hi,

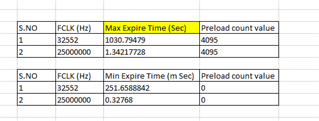

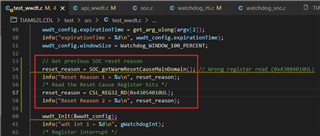

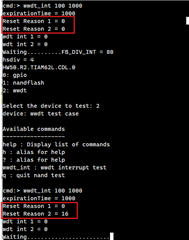

When I am running the example code F:\Example\TI\freertos_sdk_am62lx_11_00_00_05\examples\drivers\watchdog\watchdog_interrupt\am62lx-evm\a53ss0-0_nortos. I have following two quesitons.

1. �after the example binary being loaded, I am seeing "PSCI Major version 1ock_set_rate: Failed to set freq with scmi_id = 273 rate = 32552" from uart print

SOC_ModuleClockFrequency gSocModulesClockFrequency[] = {

{ AM62LX_DEV_RTI0, AM62LX_DEV_RTI0_RTI_CLK, 32552 },

{ AM62LX_DEV_UART0, AM62LX_DEV_UART0_FCLK_CLK, 48000000 },

{ SOC_MODULES_END, SOC_MODULES_END, SOC_MODULES_END },

};

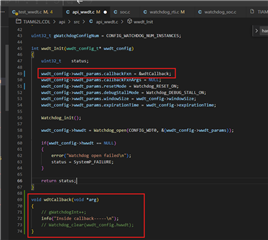

2. with expiration time set to 10000ms , should I expect the interrupt will be triggered around 10 seconds not immediately (currently it immediately triggers)?

{

.callbackFxn = NULL,

.callbackFxnArgs = NULL,

.resetMode = Watchdog_RESET_OFF,

.debugStallMode = Watchdog_DEBUG_STALL_ON,

.windowSize = Watchdog_WINDOW_100_PERCENT,

.expirationTime = 10000,

},

Thank you,

Dazong