Tool/software:

Hello, Expert

Follow title description, this is a double check.

How to let AM62x sdhci0 (eMMC0) works on SDR mode only?

Because we want to "prevent" eMMC works in DDR mode even eMMC support DDR.

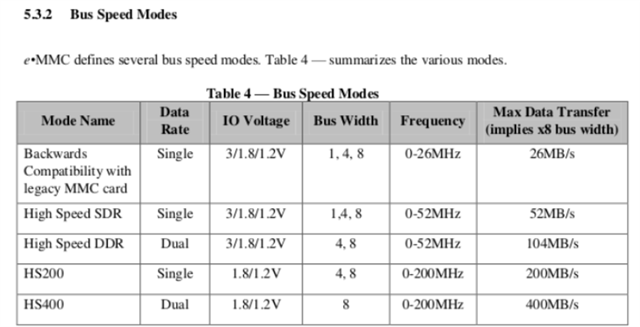

This is spec w/ AM62x

eMMC0 works w/ Legacy SDR, high speed SDR, and HS200

Base on SDK 10.00.07.04,

Linux DTS should be motify as below.

/home/gibbs/work/am62/ti-processor-sdk-linux-am62xx-evm-10.00.07.04/board-support/ti-linux-kernel-6.6.32+git-ti/arch/arm64/boot/dts/ti/k3-am62-main.dtsi

sdhci0: mmc@fa10000 {

compatible = "ti,am62-sdhci";

reg = <0x00 0x0fa10000 0x00 0x1000>, <0x00 0x0fa18000 0x00 0x400>;

interrupts = <GIC_SPI 133 IRQ_TYPE_LEVEL_HIGH>;

power-domains = <&k3_pds 57 TI_SCI_PD_EXCLUSIVE>;

clocks = <&k3_clks 57 5>, <&k3_clks 57 6>;

clock-names = "clk_ahb", "clk_xin";

assigned-clocks = <&k3_clks 57 6>;

assigned-clock-parents = <&k3_clks 57 8>;

bus-width = <8>;

/* mmc-ddr-1_8v; */

mmc-hs200-1_8v;

ti,clkbuf-sel = <0x7>;

ti,otap-del-sel-legacy = <0x0>;

ti,otap-del-sel-mmc-hs = <0x0>;

/* ti,otap-del-sel-ddr52 = <0x5>; */

ti,otap-del-sel-hs200 = <0x5>;

ti,itap-del-sel-legacy = <0xa>;

ti,itap-del-sel-mmc-hs = <0x1>;

status = "disabled";

};

UBoot DTS should be motify as below.

ti-processor-sdk-linux-am62xx-evm-10.00.07.04/board-support/ti-u-boot-2024.04+git/arch/arm/dts/k3-am62-main.dtsi

sdhci0: mmc@fa10000 {

compatible = "ti,am62-sdhci";

reg = <0x00 0x0fa10000 0x00 0x1000>, <0x00 0x0fa18000 0x00 0x400>;

interrupts = <GIC_SPI 133 IRQ_TYPE_LEVEL_HIGH>;

power-domains = <&k3_pds 57 TI_SCI_PD_EXCLUSIVE>;

clocks = <&k3_clks 57 5>, <&k3_clks 57 6>;

clock-names = "clk_ahb", "clk_xin";

assigned-clocks = <&k3_clks 57 6>;

assigned-clock-parents = <&k3_clks 57 8>;

bus-width = <8>;

/* mmc-ddr-1_8v; */

mmc-hs200-1_8v;

ti,clkbuf-sel = <0x7>;

ti,otap-del-sel-legacy = <0x0>;

ti,otap-del-sel-mmc-hs = <0x0>;

/* ti,otap-del-sel-ddr52 = <0x5>; */

ti,otap-del-sel-hs200 = <0x5>;

ti,itap-del-sel-legacy = <0xa>;

ti,itap-del-sel-mmc-hs = <0x1>;

status = "disabled";

};

Could you help us double check it?

Do I miss any thing?

Thank You Very Much

Gibbs