Other Parts Discussed in Thread: UNIFLASH, TMDSHSECDOCK-AM263

Tool/software:

This is my first question.

I bought TMDSCNCD263P and am trying to flash it by watching the academy.

I was able to flash using the command prompt.

However, when I try to flash using uniflash, I get an error and cannot do it.

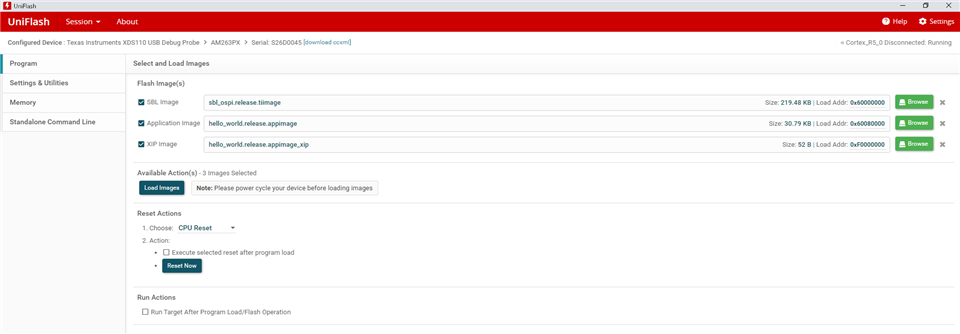

The conditions, screenshots, and error codes are as follows.

Please tell me how to solve this problem.

Condition:

・EVM:TMDSCNCD263P + TMDSHSECDOCK-AM263

・AM263Px MCU+ SDK 10.02.00

・Uniflash 8.6.0

Screenshot:

Error Code

[2025/6/4 11:48:59] [INFO] Cortex_R5_0: GEL Output: Gel files loading on R5F0 Complete [2025/6/4 11:48:59] [INFO] Cortex_R5_0: GEL Output: ***OnTargetConnect() Launched*** [2025/6/4 11:48:59] [INFO] Cortex_R5_0: GEL Output: AM263Px Initialization Scripts Launched. Please Wait... [2025/6/4 11:48:59] [INFO] Cortex_R5_0: GEL Output: AM263Px_Cryst_Clock_Loss_Status() Launched [2025/6/4 11:48:59] [INFO] Cortex_R5_0: GEL Output: Crystal Clock present [2025/6/4 11:48:59] [INFO] Cortex_R5_0: GEL Output: AM263Px_SOP_Mode() Launched [2025/6/4 11:48:59] [INFO] Cortex_R5_0: GEL Output: SOP MODE = 0x0000000B [2025/6/4 11:48:59] [INFO] Cortex_R5_0: GEL Output: DevBoot mode [2025/6/4 11:48:59] [INFO] Cortex_R5_0: GEL Output: AM263Px_Read_Device_Type() Launched [2025/6/4 11:48:59] [INFO] Cortex_R5_0: GEL Output: EFuse Device Type Value = 0x000000AA [2025/6/4 11:48:59] [INFO] Cortex_R5_0: GEL Output: AM263Px_dual_or_lockstep_mode() Launched [2025/6/4 11:48:59] [INFO] Cortex_R5_0: GEL Output: r5fss0 = 0x00000101 [2025/6/4 11:48:59] [INFO] Cortex_R5_0: GEL Output: r5fss1 = 0x00000100 [2025/6/4 11:48:59] [INFO] Cortex_R5_0: GEL Output: R5FSS0 is in Lockstep mode [2025/6/4 11:48:59] [INFO] Cortex_R5_0: GEL Output: R5FSS1 is in Lockstep mode [2025/6/4 11:48:59] [INFO] Cortex_R5_0: GEL Output: MSS_CTRL Control Registers Unlocked [2025/6/4 11:48:59] [INFO] Cortex_R5_0: GEL Output: MSS_TOP_RCM Control Registers Unlocked [2025/6/4 11:48:59] [INFO] Cortex_R5_0: GEL Output: MSS_RCM Control Registers Unlocked [2025/6/4 11:48:59] [INFO] Cortex_R5_0: GEL Output: MSS_IOMUX Control Registers Unlocked [2025/6/4 11:48:59] [INFO] Cortex_R5_0: GEL Output: TOP_CTRL Control Registers Unlocked [2025/6/4 11:48:59] [INFO] Cortex_R5_0: GEL Output: *** R5FSS0 Reset DualCore *** [2025/6/4 11:48:59] [INFO] Cortex_R5_0: GEL Output: ***R5FSS1 Reset DualCore *** [2025/6/4 11:48:59] [INFO] Cortex_R5_0: GEL Output: R5F ROM Eclipse [2025/6/4 11:48:59] [INFO] Cortex_R5_0: GEL Output: R5FSS0_0 Released [2025/6/4 11:48:59] [INFO] Cortex_R5_0: GEL Output: R5FSS0_1 Released [2025/6/4 11:48:59] [INFO] Cortex_R5_0: GEL Output: R5FSS1_0 Released [2025/6/4 11:48:59] [INFO] Cortex_R5_0: GEL Output: R5FSS1_1 Released [2025/6/4 11:48:59] [INFO] Cortex_R5_0: GEL Output: L2 Mem Init Complete [2025/6/4 11:48:59] [INFO] Cortex_R5_0: GEL Output: MailBox Mem Init Complete [2025/6/4 11:48:59] [INFO] Cortex_R5_0: GEL Output: *********** R5FSS0/1 Dual Core mode Configured******** [2025/6/4 11:49:00] [INFO] Cortex_R5_0: GEL Output: PER PLL Configuration Complete [2025/6/4 11:49:00] [INFO] Cortex_R5_0: GEL Output: SYS_CLK DIVBY2 [2025/6/4 11:49:00] [INFO] Cortex_R5_0: GEL Output: DPLL_CORE_HSDIV0_CLKOUT0 selected as CLK source for R5FSS & SYS CLKs [2025/6/4 11:49:00] [INFO] Cortex_R5_0: GEL Output: CLK Programmed R5F=400MHz and SYS_CLK=200MHz [2025/6/4 11:49:00] [INFO] Cortex_R5_0: GEL Output: *** Enabling Peripheral Clocks *** [2025/6/4 11:49:00] [INFO] Cortex_R5_0: GEL Output: Enabling RTI[0:3] Clocks [2025/6/4 11:49:00] [INFO] Cortex_R5_0: GEL Output: Enabling RTI_WDT[0:3] Clocks [2025/6/4 11:49:00] [INFO] Cortex_R5_0: GEL Output: Enabling UART[0:5]/LIN[0:5] Clocks [2025/6/4 11:49:00] [INFO] Cortex_R5_0: GEL Output: Enabling QSPI Clocks [2025/6/4 11:49:00] [INFO] Cortex_R5_0: GEL Output: Enabling I2C Clocks [2025/6/4 11:49:00] [INFO] Cortex_R5_0: GEL Output: Enabling TRACE Clocks [2025/6/4 11:49:00] [INFO] Cortex_R5_0: GEL Output: Enabling MCAN[0:3] Clocks [2025/6/4 11:49:00] [INFO] Cortex_R5_0: GEL Output: Enabling MMCSD Clocks [2025/6/4 11:49:00] [INFO] Cortex_R5_0: GEL Output: Enabling MCSPI[0:4] Clocks [2025/6/4 11:49:00] [INFO] Cortex_R5_0: GEL Output: Enabling CONTROLSS Clocks [2025/6/4 11:49:00] [INFO] Cortex_R5_0: GEL Output: Enabling CPTS Clocks [2025/6/4 11:49:00] [INFO] Cortex_R5_0: GEL Output: Enabling RGMI[5,50,250] Clocks [2025/6/4 11:49:00] [INFO] Cortex_R5_0: GEL Output: Enabling XTAL_TEMPSENSE_32K Clocks [2025/6/4 11:49:00] [INFO] Cortex_R5_0: GEL Output: Enabling XTAL_MMC_32K Clocks [2025/6/4 11:49:00] [INFO] Cortex_R5_0: GEL Output: ***All IP Clocks are Enabled*** [2025/6/4 11:49:00] [INFO] Cortex_R5_0: AM263Px [2025/6/4 11:49:01] [INFO] Executing Reset: CPU Reset [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: ***OnTargetConnect() Launched*** [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: AM263Px Initialization Scripts Launched. Please Wait... [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: AM263Px_Cryst_Clock_Loss_Status() Launched [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: Crystal Clock present [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: AM263Px_SOP_Mode() Launched [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: SOP MODE = 0x0000000B [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: DevBoot mode [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: AM263Px_Read_Device_Type() Launched [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: EFuse Device Type Value = 0x000000AA [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: AM263Px_dual_or_lockstep_mode() Launched [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: r5fss0 = 0x00000001 [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: r5fss1 = 0x00000000 [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: R5FSS0 is in Dual core mode [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: R5FSS1 is in Dual core mode [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: MSS_CTRL Control Registers Unlocked [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: MSS_TOP_RCM Control Registers Unlocked [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: MSS_RCM Control Registers Unlocked [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: MSS_IOMUX Control Registers Unlocked [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: TOP_CTRL Control Registers Unlocked [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: *** R5FSS0 Reset DualCore *** [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: ***R5FSS1 Reset DualCore *** [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: R5F ROM Eclipse [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: R5FSS0_0 Released [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: R5FSS0_1 Released [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: R5FSS1_0 Released [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: R5FSS1_1 Released [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: L2 Mem Init Complete [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: MailBox Mem Init Complete [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: *********** R5FSS0/1 Dual Core mode Configured******** [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: SYS_CLK DIVBY2 [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: DPLL_CORE_HSDIV0_CLKOUT0 selected as CLK source for R5FSS & SYS CLKs [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: CLK Programmed R5F=400MHz and SYS_CLK=200MHz [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: *** Enabling Peripheral Clocks *** [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: Enabling RTI[0:3] Clocks [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: Enabling RTI_WDT[0:3] Clocks [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: Enabling UART[0:5]/LIN[0:5] Clocks [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: Enabling QSPI Clocks [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: Enabling I2C Clocks [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: Enabling TRACE Clocks [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: Enabling MCAN[0:3] Clocks [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: Enabling MMCSD Clocks [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: Enabling MCSPI[0:4] Clocks [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: Enabling CONTROLSS Clocks [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: Enabling CPTS Clocks [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: Enabling RGMI[5,50,250] Clocks [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: Enabling XTAL_TEMPSENSE_32K Clocks [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: Enabling XTAL_MMC_32K Clocks [2025/6/4 11:49:02] [INFO] Cortex_R5_0: GEL Output: ***All IP Clocks are Enabled*** [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: ***OnTargetConnect() Launched*** [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: AM263Px Initialization Scripts Launched. Please Wait... [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: AM263Px_Cryst_Clock_Loss_Status() Launched [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: Crystal Clock present [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: AM263Px_SOP_Mode() Launched [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: SOP MODE = 0x0000000B [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: DevBoot mode [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: AM263Px_Read_Device_Type() Launched [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: EFuse Device Type Value = 0x000000AA [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: AM263Px_dual_or_lockstep_mode() Launched [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: r5fss0 = 0x00000101 [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: r5fss1 = 0x00000100 [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: R5FSS0 is in Lockstep mode [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: R5FSS1 is in Lockstep mode [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: MSS_CTRL Control Registers Unlocked [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: MSS_TOP_RCM Control Registers Unlocked [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: MSS_RCM Control Registers Unlocked [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: MSS_IOMUX Control Registers Unlocked [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: TOP_CTRL Control Registers Unlocked [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: *** R5FSS0 Reset DualCore *** [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: ***R5FSS1 Reset DualCore *** [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: R5F ROM Eclipse [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: R5FSS0_0 Released [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: R5FSS0_1 Released [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: R5FSS1_0 Released [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: R5FSS1_1 Released [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: L2 Mem Init Complete [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: MailBox Mem Init Complete [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: *********** R5FSS0/1 Dual Core mode Configured******** [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: PER PLL Configuration Complete [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: SYS_CLK DIVBY2 [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: DPLL_CORE_HSDIV0_CLKOUT0 selected as CLK source for R5FSS & SYS CLKs [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: CLK Programmed R5F=400MHz and SYS_CLK=200MHz [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: *** Enabling Peripheral Clocks *** [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: Enabling RTI[0:3] Clocks [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: Enabling RTI_WDT[0:3] Clocks [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: Enabling UART[0:5]/LIN[0:5] Clocks [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: Enabling QSPI Clocks [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: Enabling I2C Clocks [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: Enabling TRACE Clocks [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: Enabling MCAN[0:3] Clocks [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: Enabling MMCSD Clocks [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: Enabling MCSPI[0:4] Clocks [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: Enabling CONTROLSS Clocks [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: Enabling CPTS Clocks [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: Enabling RGMI[5,50,250] Clocks [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: Enabling XTAL_TEMPSENSE_32K Clocks [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: Enabling XTAL_MMC_32K Clocks [2025/6/4 11:49:13] [INFO] Cortex_R5_0: GEL Output: ***All IP Clocks are Enabled*** [2025/6/4 11:49:34] [ERROR] Cortex_R5_0: Run failed... [2025/6/4 11:49:34] [ERROR] Cortex_R5_0: File Loader: Memory write failed: Timed out waiting for target to halt while executing am263px_flasher.out