Other Parts Discussed in Thread: AM69, SYSCONFIG, TDA4VH

Tool/software:

Hello TI experts,

We are using a custom hardware platform based on the AM69A and are currently conducting multiple reboot tests.

During this process, we have observed two recurring boot issues that intermittently prevent the board from booting:

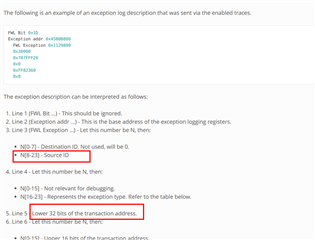

1. SPL hang due to frequency handshake timeout:

U-Boot SPL 2024.04-ti-gcedb677ccf6e (Apr 25 2025 - 10:55:48 +0000) SYSFW ABI: 4.0 (firmware rev 0x000b '11.0.9--v11.00.09+ (Fancy Rat)') Timeout during frequency handshake ### ERROR ### Please RESET the board ###

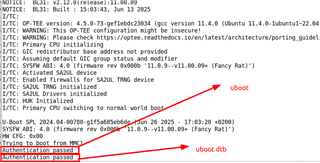

2. Hang during SPL to U-Boot proper transition:

U-Boot SPL 2024.04-34430-gf8c18ba41a3-dirty (May 16 2025 - 08:41:36 +0200) SYSFW ABI: 4.0 (firmware rev 0x000b '11.0.9--v11.00.09+ (Fancy Rat)') Initialized 4 DRAM controllers SPL initial stack usage: 13456 bytes HW CFG: 0x 0 Trying to boot from MMC1 Authentication passed Authentication passed Authentication passed Loading Environment from nowhere... OK init_env from device 17 not supported! Authentication passed Authentication passed Starting ATF on ARM64 core... NOTICE: BL31: v2.11.0(release):v2.11.0-906-g58b25570c9-dirty NOTICE: BL31: Built : 04:20:32, Nov 1 2024 I/TC: I/TC: OP-TEE version: 4.4.0-dev (gcc version 13.3.0 (GCC)) #1 Fri Oct 18 17:45:27 UTC 2024 aarch64 I/TC: WARNING: This OP-TEE configuration might be insecure! I/TC: WARNING: Please check https://optee.readthedocs.io/en/latest/architecture/porting_guidelines.html I/TC: Primary CPU initializing I/TC: GIC redistributor base address not provided I/TC: Assuming default GIC group status and modifier I/TC: SYSFW ABI: 4.0 (firmware rev 0x000b '11.0.9--v11.00.09+ (Fancy Rat)') I/TC: Activated SA2UL device I/TC: Enabled firewalls for SA2UL TRNG device I/TC: SA2UL TRNG initialized I/TC: SA2UL Drivers initialized I/TC: HUK Initialized I/TC: Primary CPU switching to normal world boot U-Boot SPL 2024.04-34430-gf8c18ba41a3-dirty (May 16 2025 - 08:42:40 +0200) SYSFW ABI: 4.0 (firmware rev 0x000b '11.0.9--v11.00.09+ (Fancy Rat)') HW CFG: 0x 0 Trying to boot from MMC1 Authentication passed Authentication passed ------- Hangs here -------

Our design closely mirrors the AM69 SK board in terms of DDRSS layout/config and software stack.

We came across a potentially related issue in the TI E2E forum:

https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1308890/tda4vh-q1-timeout-during-frequency-handshake/5211296#5211296

We experimented with the mentioned DDRSS parameter changes in above thread, which slightly improved behavior. However, corresponding Eye Diagrams show degraded signal integrity compared to the original configuration, so we do not plan to adopt those changes without stronger evidence.

Could you help us understand potential root causes for these boot issues?

Any guidance or suggestions would be highly appreciated.

Regards,

Parth P