Other Parts Discussed in Thread: AM6421

Tool/software:

Hi,

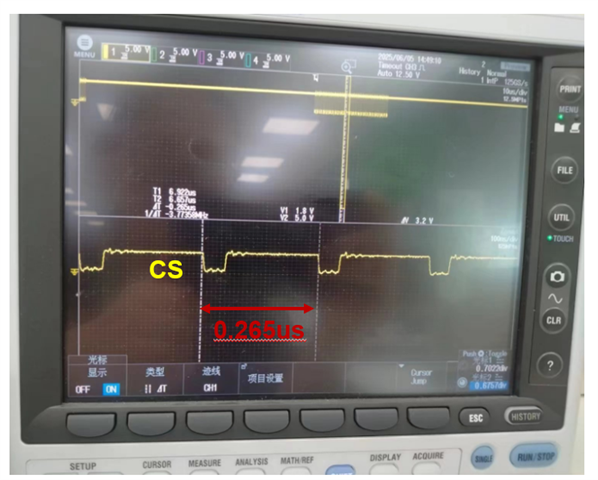

when using AM6421 GPMC to communicate with FPGA, the time delay between two reads seems very long. in the test, the delay is around 0.26us as shown in the following picture. the yellow line is the CS signal.

my questions are:

1 why the delay between two reads are so long, even though we set the cycle delay to NO Delay?

2 how can we reduce the time delay between two reads?

3 the same delay is shown between two writes. how to reduce the time delay between two writes?

we do not want to use GPMC burst mode because there will be a lot of work on FPGA coding.

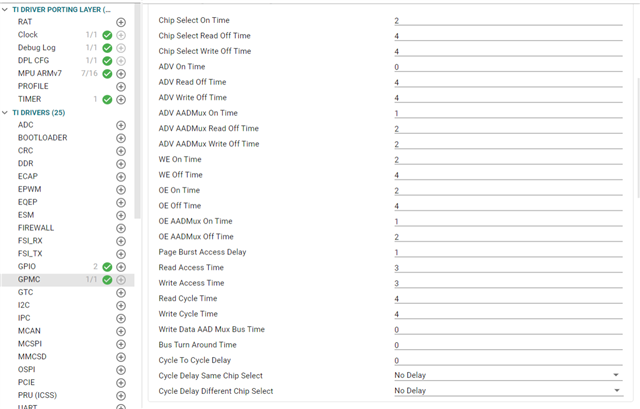

The GPMC config is as following.

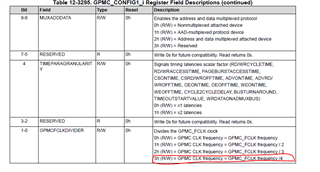

synchronous single write and read mode are configured. wait pin is enabled. the timing parameter is as following

and the read from FPGA code is as following:

volatile uint16_t *pSrc = (volatile uint16_t *)(OFFSET + BASEADDRESS_CS0);

volatile uint16_t *pDst = (volatile uint16_t *)test_gpmcRxBuf;

for(i = 0; i<16; i++)

{

*pDst = *pSrc;

pSrc++;

pDst++;

}

thank you!