Other Parts Discussed in Thread: DRA821

Tool/software:

Hello,

I am using an DRA821 processor and implementing the single PMIC power scheme using the document "slvucd4.pdf".

The question I have is the pull-up power rail for GPIO6.

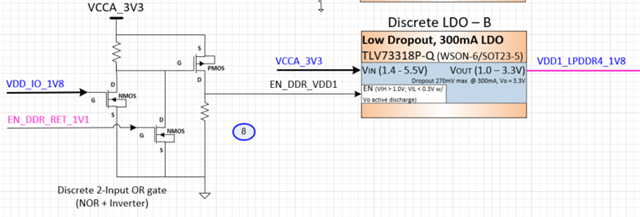

The document refers to this signal as name as EN_DDR_RET_1V1, and suggests the pull-up power rail to be VDD_DDR_1V1_REG.

This is used to enable an LDO to provide the power rail VDD1_LPDDR4_1V8.

This would mean that the DDR 1V1 rail would precede the DDR 1V8 rail.

I think this is a mistake.

LPDDR4 requires the 1V8 rail to be powered BEFORE the 1V1 rail.

NOTE: I DO NOT intend to use DDR retention in my design.

Q1/ Can I enable the DDR 1V8 LDO with the power rail VDD_IO_1V8 (PMIC LDO1) ?

Q2/ Instead can i wire the power rail VDD_IO_1V8 (PMIC LDO1) directly to the DDR4 1V8 pins ?

Q3/ How should I wire up the CPU pin DDR_RET (ball # R5) ?

Thanks,

Steve