Tool/software:

Hello,

I have some questions related to the memory usage of the UBOOT R5 SPL and the UBOOT A72 SPL.

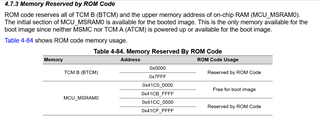

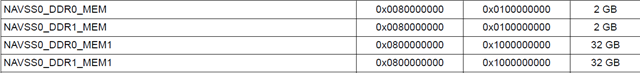

When I build the U-Boot R5 SPL and I check the corresponding map file, I find the start address 0x0000000080800000. According to the technical Reference Manual this would be the DDR memory range is that correct?

If yes, could you tell me which code part is initializing the DDR before the UBOOT R5 SPL is running?

Also in the linker file for the UBOOT A72 SPL I see the following definitions in the linker script:

MEMORY { .sram : ORIGIN = 0x80080000

Is that address really located in the SRAM? Where can I see that in the rechnical reference manual?

Thank you very much in advance.