Tool/software:

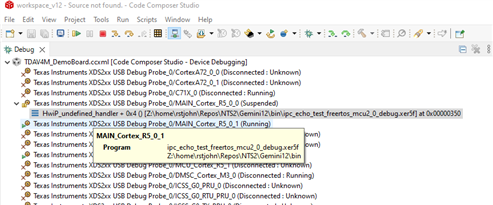

I have the large Common Carrier Board with a J721EXSOMXEVM processor card installed. I am loading and running the programs from a JTAG connection with a TI XDS200 jtag probe. We have built and run other code using this method.

I am trying to run a modified IPC echo example on two R5 cores only. Main MCU2_0 and Main MCU2_1. ( I won't get into the confusion naming of the MCU's at this time. )

I took the stock ipc_echo_test_freertos example and just limited it to those two cores by editing the "ipc_rtos_echo_test.c" file for those two cores to the following.

#if defined (SOC_J721E)

#define CORE_IN_TEST 1

.....

#ifdef BUILD_MCU2_0

uint32_t selfProcId = IPC_MCU2_0;

uint32_t remoteProc[] =

{

#if defined (SOC_J721E)

IPC_MCU2_1

.....

#ifdef BUILD_MCU2_1

uint32_t selfProcId = IPC_MCU2_1;

uint32_t remoteProc[] =

{

#if defined (SOC_J721E)

IPC_MCU2_0

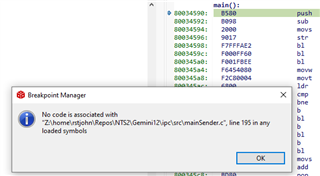

I spend half my time fighting with Code Composer Studio and the debugger and the other half setting breakpoints in assembly becasue it refuses to let me put breakpoints in the c code.