Tool/software:

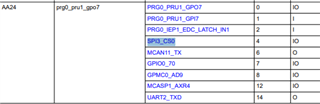

I've moved on to a full J721E board with the SOM from a TVA4VM board, now accessing MCSPI3 and MCSPI6 through the GESI board. I'm using MCU2_1, FreeRTOS, using the 10.x TI SDK w/ PDK.

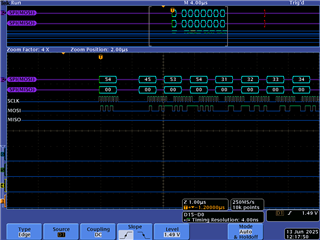

I've observed I can successfully transmit and receive on each, but in every case I've tried, I'm only transmitting one byte. I would expect there to be the entire message.

Task launched:

void spi_test_master_cb(void *arg0, void *arg1)

{

UART_printf("Starting SPI Master test. \n");

TaskP_sleepInMsecs(1000);

uint32_t terminateXfer = 1;

SPI_init();

// == Set up the SPI test for receive ==

SPI_Handle spi;

SPI_Params spiParams;

// Creates a callback semaphore

SPI_osalSemParamsInit(&cbSemParams);

cbSemParams.mode = SemaphoreP_Mode_BINARY;

cbSem[0] = SPI_osalCreateBlockingLock(0, &cbSemParams);

uint32_t instance = MCSPI3_CONFIG_IDX;

uint32_t domain = SPI_MCSPI_DOMAIN_MAIN;

// MCSPI_socInit();

SPI_HWAttrs spi_cfg;

SPI_socGetInitCfg(domain, instance, &spi_cfg);

spi_cfg.enableIntr = BFALSE;

spi_cfg.edmaHandle = NULL;

spi_cfg.dmaMode = BFALSE;

/* Set the SPI init configurations */

spi_cfg.chNum = 0;

spi_cfg.chnCfg[0].dataLineCommMode = MCSPI_DATA_LINE_COMM_MODE_6;

spi_cfg.chnCfg[0].tcs = MCSPI_CS_TCS_0PNT5_CLK;

spi_cfg.chnCfg[0].trMode = MCSPI_TX_ONLY_MODE;

/* Set the SPI init configurations */

SPI_socSetInitCfg(domain, instance, &spi_cfg);

/* Initialize SPI handle */

SPI_Params_init(&spiParams);

spiParams.mode = SPI_MASTER;

spiParams.transferMode = SPI_MODE_BLOCKING;

spiParams.transferTimeout = SemaphoreP_WAIT_FOREVER;

spiParams.frameFormat = SPI_POL1_PHA0;

spiParams.dataSize = 8U; // 8 bits

spiParams.bitRate = 468750;

spi = SPI_open(domain, instance, &spiParams);

if (NULL == spi)

{

UART_printf("Error initializing SPI\n");

return;

}

uint32_t num_xfers = 0;

uint32_t xfer_len = SPI_MSG_LENGTH; //8

Osal_delay(500);

// Attempt a transfer

// uintptr_t addrMasterRxBuf = (uintptr_t)masterRxBuffer;

uintptr_t addrMasterTxBuf = (uintptr_t)masterTxBuffer;

bool transferOK = true;

// memset(masterRxBuffer, 0, sizeof(masterRxBuffer));

memset(masterTxBuffer, 0, sizeof(masterTxBuffer));

while (1)

{

memcpy(masterTxBuffer, "TEST1234", 8);

SPI_Transaction transaction;

transaction.count = xfer_len;

transaction.arg = (void *)&terminateXfer;

transaction.txBuf = (void *)addrMasterTxBuf;

transaction.rxBuf = NULL; // (void *)addrMasterRxBuf;

transferOK = SPI_transfer((SPI_Handle)spi, &transaction);

if (!transferOK)

{

UART_printf("Error in SPI transfer\n");

}

else

{

UART_printf("SPI transfer successful.\n");

}

Osal_delay(10);

}

}

I've discovered if I enable TURBO mode, I get two bytes, but I never get the whole message. Also if I change 'dataSize' in the SPI_Params struct, it does seem to scale to two bytes, but it's impractical for larger messages.

Other things I've tinkered with but didn't see a change/couldn't get working:

* Increasing the bitrate.

* Adjusting the txTrigLvl in the SPI_HWAttrs.

Any ideas what else I should try, or do you see a setting here that isn't correct?