Other Parts Discussed in Thread: CDCEL937, CDCE925

Tool/software:

Hi, TI expert,

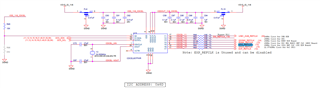

We find a issue that the voltage of CSI2_REFCLK is lower as 0.8V on TDA4AL EVM.

But in schematic as below, it voltage should be 1.8V, I think this pin output not work seems in Hi-Z status.

In ti-processor-sdk-rtos-j721s2-evm-10_01_00_04, I try to find the related function of i2c0.

Only find the definition in board_cfg.h, code path is "pdk_j721s2_10_01_00_25\packages\ti\board\src\j721s2_evm\include"

#define BOARD_I2C_PERI_CLOCK_GENERATOR (0x6D)

Could you help us to point how do I check this "PERIPHERAL CLOCK GENERATOR" work or not?

Thnaks,

YL