Tool/software:

May I ask if the driving strength of the eMMC can be adjusted? If so, how can it be configured? We are currently observing signal attenuation on the CLK line, and the CLK frequency is 200 MHz.

Tool/software:

May I ask if the driving strength of the eMMC can be adjusted? If so, how can it be configured? We are currently observing signal attenuation on the CLK line, and the CLK frequency is 200 MHz.

I misread your post and thought you were asking how to attenuate the signal. I didn't understand why you would want to do that. Now I understand, you are concerned with the reduced amplitude.

Why do you feel this is a problem? The signal amplitude has significant margin over the VIL (0.35% VDD = 0.63V) and VIH (0.65% VDD = 1.17V) levels defined in the eMMC standard.

Regards,

Paul

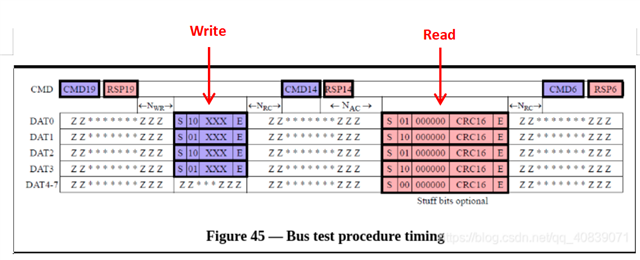

I assume you are trying to operate at HS200 since CLK is toggling at 200MHz. The eMMC standard requires an eMMC device to operate with a minimum of 1.40ns of setup and 0.8ns of hold. You should not have a problem as long as the CLK to DAT/CMD delay relationship meets these requirements.

Are you using the latest release of software? You should be using the latest software driver because the software team has made some updates that may impact timing. Please tell me what software you are using, and I will assign this E2E thread to the appropriate team to help answer this question.

You may need to extract PCB trace characteristics from your current PCB design and use them along with the IBIS models of both devices to perform a signal integrity analysis if the signals are still not meeting the eMMC device input requirements after confirming you have the latest software driver. It may be necessary to make adjustments to your PCB design in the simulation environment to determine what is necessary to improve your signal integrity.

The SDK11.1 has a sw bug fix in the kernel MMC driver which corrects the timing for certain situations. So please check your use case with SDK11.1 kernel to see if the issue still happens.

Can you attach a scope capture that shows the clock to data relationship? Make sure you are probing near the eMMC device using a high bandwidth scope with two high bandwidth scope probes that have been de-skewed. I would like to see the setup/hold margin being provided to the eMMC device.

Regards,

Paul

The host is providing plenty of setup and hold time margin to the eMMC device during write operations. You are not able to measure setup and hold time for read operations since the AM62x device captures read data with an internally delayed clock that is positioned in the center of the data valid window by a tuning algorithm.

Regards,

Paul

What is happening when you say the peripheral is not working at 200MHz? Is it completely broken, or is it intermittent? How many PCB assemblies have been tested? Do they all experience the same symptoms?

Are you able to read/write data to the attached eMMC device without any issue at a reduced operating frequency? If so, you could potentially try various combinations of reduced rate read/write operations to determine if the issue you are having is associated with reading or writing data at the faster rate.

Can you capture the software log when the failure occurs? If so, this may provide some insight into what is happening.

Regards,

Paul

How can I determine when the response occurs? I want to verify the timing when the eMMC sends a signal back to the AM62.

I was on vacation for several days and just seeing your latest question, which I do not understand. I'm not sure what you are asking?

You will not be able to verify timing to the AM62x device because the receiver in the AM62x device is adjusting its capture clock position relative to read data to capture valid data. The appropriate delay is determined by a software tuning algorithm and varies based on the AM62x process/voltage/temperature operating conditions, your PCB delays, and the attached device process/voltage/temperature operating conditions.

FYI: We recently had another customer reporting issues with HS200 operation on AM62x and found their PCB had too much power supply noise on the VDDSHV4 power rail. Do you have a decoupling capacitor connected directly to pin T7?

Regards,

Paul